*GE Power Management Technical Notes*

## Breaker Arc Detection Scheme in UR Relays

**GE Publication No. GET-8404**

Copyright © 2002 GE Power Management

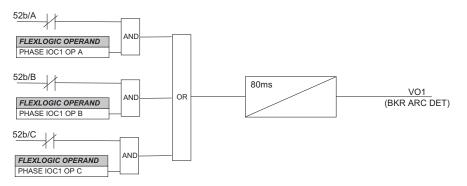

The conditions that prove an arc condition concerning a circuit breaker (flashover) are: open breaker and presence of current in any phase. The arc detector can easily be build in FlexLogic<sup>™</sup>. An overcurrent element (IOC) with a low setting will be used for current detection. As a substitute for IOC, three FlexElements<sup>™</sup> can be used for current detection in all three phases.

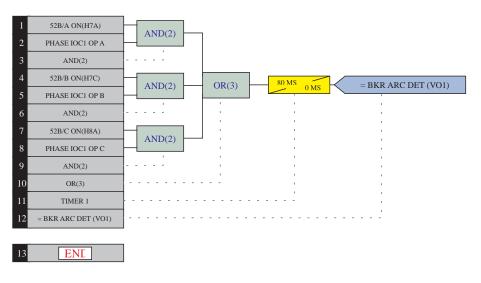

The logic can be per phase discriminated or can use a single input from breaker auxiliary contacts to determine breaker status, when the breaker is three pole operated. The following example presents a single pole discriminated logic:

The timer should introduce a delay to avoid false signals due to a possible race between breaker auxiliary contacts operation and reset of the overcurrent elements. Virtual Output 1 can be used to send an alarm.

To implement the Breaker Arc Detection scheme in FlexLogic<sup>™</sup>, make the following settings changes:

| 🚥 Contact Inputs // UR: Test Rig: Settings: Inputs/Outputs |          |          |          |           |  |  |  |

|------------------------------------------------------------|----------|----------|----------|-----------|--|--|--|

| 1 2 x 2 8 8 8 8                                            |          |          |          |           |  |  |  |

| PARAMETER                                                  | H7A      | H7C      | H8A      | H8C       |  |  |  |

| JQ.                                                        | 52b/A    | 52b/B    | 52b/C    | Cont lp 4 |  |  |  |

| evyents                                                    | Disabled | Disabled | Disabled | Disabled  |  |  |  |

| Test Rig Settings: Inputs/Outputs                          |          |          |          |           |  |  |  |

| Flexlogic Tir                | ners // UR: Te |  |  |  |  |

|------------------------------|----------------|--|--|--|--|

| PARAMETER                    | TIMER 1        |  |  |  |  |

| Туре                         | millisecond    |  |  |  |  |

| Pickup Delay                 | 80             |  |  |  |  |

| Dropout Delay                | 0              |  |  |  |  |

| •                            |                |  |  |  |  |

| Test Rig Settings: Flexlogic |                |  |  |  |  |

| Virtual Outputs // UR: Test Rig: Sett |                         |  |  |  |  |  |

|---------------------------------------|-------------------------|--|--|--|--|--|

| $\mathscr{I} \supseteq \mathbb{X}$    | 2   9   8   8           |  |  |  |  |  |

| PARAMETER                             | VIRTUAL OUTPUT 1        |  |  |  |  |  |

| ID                                    | BKR ARC DET             |  |  |  |  |  |

| Events                                | Disabled                |  |  |  |  |  |

| •                                     |                         |  |  |  |  |  |

| 🕥 Test Rig 🛛 Se                       | ettings: Inputs/Outputs |  |  |  |  |  |

| 10)         |               |  |  |  |  |

|-------------|---------------|--|--|--|--|

| PARAMETER   | PHASE IOC1    |  |  |  |  |

| Function    | Enabled       |  |  |  |  |

| Source      | SRC x (SRC 1) |  |  |  |  |

| Pickup      | 0.200 pu      |  |  |  |  |

| Delay       | 0.00 s        |  |  |  |  |

| Reset Delay | 0.00 s        |  |  |  |  |

| Block A     | OFF           |  |  |  |  |

| Block B     | OFF           |  |  |  |  |

| Block C     | OFF           |  |  |  |  |

| Target      | Self-reset    |  |  |  |  |

| Events      | Disabled      |  |  |  |  |

| LVCIILS     | Disabica      |  |  |  |  |

The FlexLogic<sup>™</sup> implementation is shown below: