# STATIC OUTPUT AND TRIPPING UNIT

**TYPE SLAT51AF**

# GEK-86088

# CONTENTS

|       |                                                      |                |                           |                      |                  |                |                 |                |                   |             |                   |         |             |        |                |                   |                                       |   |     |     |   |            |     |       |   |     |   |   |   |     |            |   |   |   |       | <u>P</u> . | AGE                             |

|-------|------------------------------------------------------|----------------|---------------------------|----------------------|------------------|----------------|-----------------|----------------|-------------------|-------------|-------------------|---------|-------------|--------|----------------|-------------------|---------------------------------------|---|-----|-----|---|------------|-----|-------|---|-----|---|---|---|-----|------------|---|---|---|-------|------------|---------------------------------|

| DESCI | RIPI                                                 | ГІО            | N                         | •                    |                  |                |                 |                |                   | •           | •                 | •       |             |        |                |                   |                                       |   | •   |     | • | •          | • • |       | • | •   |   | • | • |     |            | • | • |   |       | •          | 3                               |

| APPL  | ICAT                                                 | ΓΙΟ            | N                         | •                    |                  |                |                 | •              |                   | •           |                   |         |             |        | •              |                   |                                       |   |     |     | • | •          |     |       |   | •   |   |   |   |     |            |   |   |   |       |            | 3                               |

| RATI  | NGS                                                  |                |                           |                      |                  |                |                 |                |                   | •           | •                 | •       |             | •      | •              |                   |                                       |   |     |     | • |            |     |       |   | •   |   |   | • |     |            | • | • | • |       |            | 4                               |

|       | TAE                                                  |                |                           |                      |                  |                |                 |                |                   |             |                   |         |             |        |                |                   |                                       |   |     |     |   |            |     |       |   |     |   |   |   |     |            |   |   |   |       |            | 4<br>4                          |

| BURD  | ENS                                                  |                |                           |                      |                  |                |                 |                |                   | •           |                   | • •     |             | •      | •              |                   |                                       | • |     |     |   | •          |     |       |   | •   |   |   | • | • • |            | • | • |   |       |            | 5                               |

|       | SCF<br>NOF<br>RI<br>BF1<br>OP1                       | RMA<br>RE<br>B | L L<br>C L<br>R E         | Y<br>0:              | 0<br>S E<br>K E  | P E            | E N<br>I N<br>F | I<br>A         | C C<br>T I<br>I L | N<br>A<br>U | T /<br>T I<br>R I | A(<br>E | T<br>C<br>I | I<br>N | TF<br>R(<br>I) | R I<br>C U<br>T I | P<br>I<br>A                           | T | C : | r R | C | U :<br>R ( | ΙΊ  | Γ<br> | · | • • |   |   |   |     | • •        | • | • | • | • •   |            | 5<br>5<br>5<br>5<br>5           |

| TARGE | ETS                                                  |                |                           | •                    |                  | •              |                 | •              |                   | •           | •                 |         | •           | •      |                |                   | •                                     | • |     |     | • |            |     |       | • |     |   | • | • |     |            | • | • |   |       |            | 6                               |

| LOGIC | C C I                                                | RC             | UΙ                        | T                    | S                |                |                 |                |                   |             | •                 |         | •           | •      | • •            |                   |                                       | • |     |     | • | •          |     | •     | • |     |   | • | • |     | . <b>.</b> |   | • | • |       |            | 6                               |

| CALCU | JLAT                                                 | .10            | N                         | 01                   | =                | SE             | ΞT              | T.             | [ N               | G           | S                 |         | •           |        |                |                   |                                       |   | •   |     |   |            |     |       |   |     |   | • |   |     |            | • | • |   |       |            | 6                               |

| CONST | ruc                                                  | ΤI             | ON                        | ١.                   |                  |                |                 | •              |                   |             | •                 |         | •           | •      |                |                   |                                       | • |     |     |   |            |     |       |   |     |   |   |   |     |            |   |   |   |       |            | 6                               |

| RECEI | VIN                                                  | IG,            | Н                         | A                    | ۱D               | L 1            | N               | G              | A                 | N           | D                 | S       | T           | 01     | R A            | ۱G                | Ε                                     |   |     |     |   |            |     |       |   |     |   |   |   |     |            | • |   |   |       |            | 7                               |

| TEST  | INS                                                  | TR             | UC                        | Τ]                   | 0 ]              | N S            | ;               | •              |                   |             |                   |         | •           |        |                |                   |                                       | • |     |     |   |            |     |       |   |     | • |   |   |     |            |   |   |   |       |            | 7                               |

|       | CAU<br>GEN<br>OPE<br>TES<br>TIM<br>TAB<br>TRI<br>OVE | ERATIER LE     | AL<br>TI<br>CA<br>I<br>CI | 01<br>RI<br>DI<br>II | )<br>[<br>[<br>U | L<br>AC<br>S T | CAM             | HE<br>PT<br>EN | EC<br>TE<br>NT    | K<br>R<br>S | s<br>S            | A N     | i D         | •      | TE             | S .               | · · · · · · · · · · · · · · · · · · · | • | • • | • • |   | • •        | • • |       |   | • • |   |   |   | • • | • •        |   |   | • | • • • |            | 7<br>8<br>8<br>8<br>8<br>9<br>9 |

| MAINT | ENA                                                  | NC             | Ε                         |                      |                  |                | •               |                | •                 |             |                   |         |             |        |                |                   | •                                     |   |     |     | • |            |     | •     |   |     |   |   | • |     |            |   | • | • |       | 1          | lΟ                              |

|       | PER<br>TRO<br>SPA                                    | UB             | LΕ                        | Sŀ                   | 10               | 0 T            | I               | NG             | ì                 |             |                   |         |             |        |                |                   |                                       |   |     |     |   |            |     |       |   |     |   |   |   |     |            |   |   |   |       | 1          |                                 |

#### STATIC OUTPUT AND TRIPPING UNIT

#### TYPE SLAT51AF

#### DESCRIPTION

The Type SLAT51AF relay is a static output and tripping unit. The relay is not intended to be used by itself, but rather as part of a complement of equipment that forms a protective relaying scheme. For a complete description of the overall scheme in which this relay is employed, refer to the overall logic diagram and its associated logic description that is supplied with each terminal of equipment.

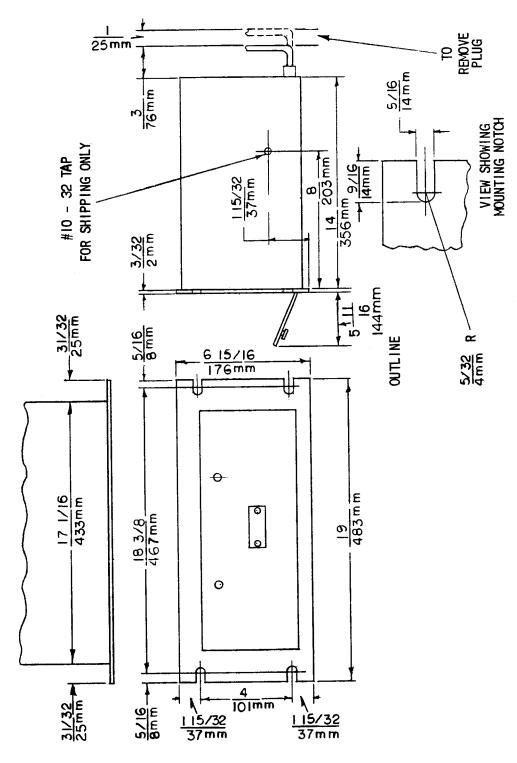

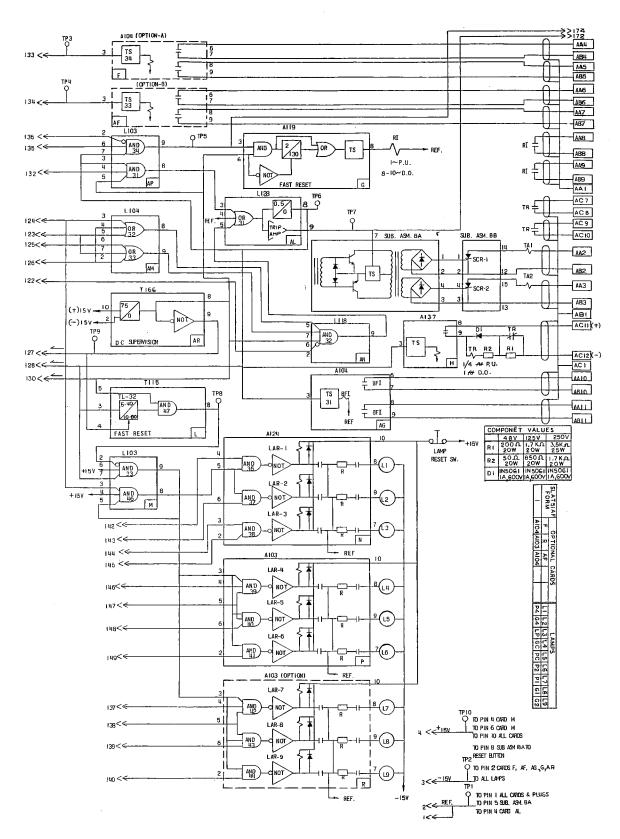

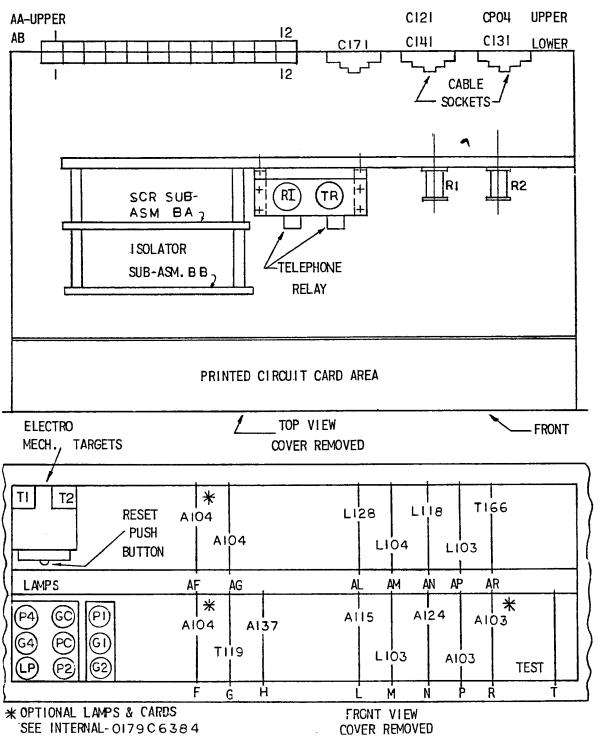

The Type SLAT51AF relay is packaged in a four-rack unit (one rack unit equals 1--3/4 inches) enclosed metal case suitable for mounting on a 19--inch rack. The outline and mounting dimensions are shown in Figure 1. The internal connections for the relay are shown in Figure 2. The component and card locations are shown in Figure 3.

#### APPLICATION

The Type SLAT51AF relay is a static output and tripping relay designed for use in a variety of schemes. For example, the SLAT51AF relay can be used with types SLY, SLYG, SLC, SSA and SLA relays to make up a directional comparison unblocking or permissive overreaching transferred tripping scheme. For a complete description of the application of this relay in a particular scheme, refer to the logic description and diagram supplied with the scheme. The following is a list of the various functions included in the relay together with a general description of their intended uses.

- SCR Two silicon controlled rectifier trip circuits are provided to permit tripping of associated circuit breakers.

- RI The reclose initiation outputs are provided to initiate automatic reclosing after a high speed trip.

- BFI The breaker failure initiation outputs are provided for breaker failure protection.

- T1, T2 Electromechanical targets that give an indication when the associated trip SCR passes trip current.

- TARGET LAMPS Provide an indication of the function that initiated tripping.

- OPTIONAL Two sets of two output contacts each are provided for the customer's specific application.

Two normally open telephone relay trip circuits are provided to permit tripping of associated circuit breakers. These contacts are electrically separate.

These instructions do not purport to cover all details or variations in equipment nor to provide for every possible contingency to be met in connection with installation, operation or maintenance. Should further information be desired or should particular problems arise which are not covered sufficiently for the purchaser's purposes, the matter should be referred to the General Electric Company.

To the extent required the products described herein meet applicable ANSI, IEEE and NEMA standards; but no such assurance is given with respect to local codes and ordinances because they vary greatly.

#### RATINGS

The Type SLAT51AF relay is designed for use in an environment where the air temperature outside the relay case does not exceed minus  $20^{\circ}$ C and plus  $65^{\circ}$ C.

The Type SLAT51AF relay requires a plus or minus 15 volt DC power source which can be obtained from a Type SSA power supply.

The SCR tripping circuits are rated for 48/125 or 250 volts DC. Each has a 1.0 ampere series target. The tripping circuits are designed to carry 30 amperes for one second.

All of the following contacts are rated for 48/125/250 volts DC. The tripping circuits are designed to carry 30 amperes for one second (three amperes resistive, continuous). See Table I.

The ratings for the RI relay are listed in Table I, and the ratings of the BFI and optional output contacts are listed in Table II.

Refer to the unit nameplate for the ratings of a particular relay.

# TABLE I

|     | ABSOLUTE       | E MAXIMUM RATINGS                            |  |

|-----|----------------|----------------------------------------------|--|

| 180 | VA Resistive   | )                                            |  |

| 60  | VA Inductive** | )— Interruption<br>) Capacity                |  |

|     |                | and carry continuous<br>and carry short time |  |

#### TABLE II

|        | ABSOLUTE    | MAXIMUM RATINGS                              |

|--------|-------------|----------------------------------------------|

| 100 VA | Resistive   | )<br>Interputtion                            |

| 35 VA  | Inductive** | <pre>)— Interruption ) Capacity</pre>        |

|        |             | and carry continuous<br>and carry short time |

<sup>\*\*</sup>The inductive rating is based on the inductance of a coil having an  $X_L/R$  ratio of three to one.

#### BURDENS

The SLAT51AF relay presents a maximum burden to the Type SSA power supply of:

250 milliamperes from the plus 15 volt DC supply 130 milliamperes from the minus 15 volt DC supply

In addition, each target lamp draws 80 milliamperes from the minus 15 volt DC power supply.

# SCR TRIP CIRCUIT

Two electrically separate, isolated SCR trip circuits are provided to trip two breakers.

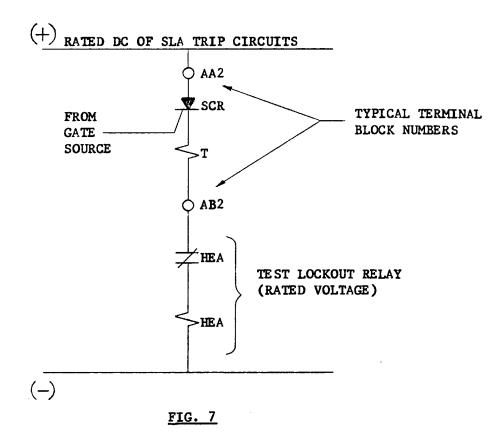

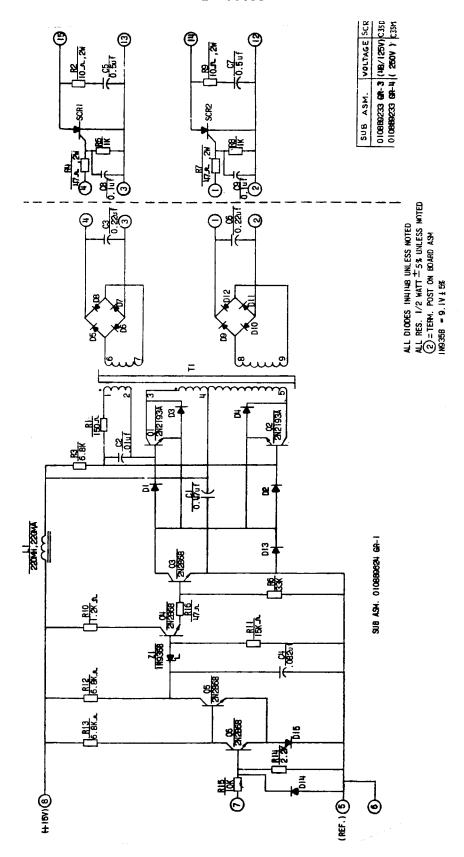

The internal connections for the SCR trip and isolator subassemblies are shown in Figure 6. The isolator card, by means of a DC-to-DC converter, provides a signal path, but maintains metallic isolation. This feature makes it possible to isolate the relay power supply from the trip circuit power supply.

# NORMALLY OPEN CONTACT TRIP CIRCUIT

Two electrically separate, isolated normally open contact trip circuits are provided to trip two breakers. Each circuit is capable of carrying 30 amperes for one second (see Table I). The telephone-type relay is designed to operate from 48, 125 or 250 volts DC, depending on the model. The pickup time of this relay is 4-4.7 milliseconds from the time its coil is energized. The dropout time is 16-20 milliseconds from the time its coil is de-energized.

# RI RECLOSE INITIATE CIRCUIT

Two electrically separate, normally open contacts are provided. These contacts close within 16 milliseconds from the time the associated coil is energized by the logic. These contacts open within 160 milliseconds from the time the coil is deenergized. The RI function uses a telephone-type relay with contact ratings stated under RATINGS.

# BFI BREAKER FAILURE INITIATE CIRCUIT

Two electrically separate, normally open contacts are provided. These contacts close within two milliseconds from the time the associated coil is energized by the logic. These contacts open within two milliseconds from the time the coil is deenergized. The BFI function uses a reed relay with contact ratings stated under RATINGS.

# OPTIONAL OUTPUTS

Four optional reed relay contact outputs can be provided in either normally open or normally closed configuration. The contacts operate within two milliseconds from the time logic signals, available from the selected matrix points in the associated SLA, change state.

#### **TARGETS**

Two electromechanical target coils are included, one in series with each trip SCR. These targets operate on one ampere of trip current when the associated trip SCR passes current. The trip circuit resistance in the relay is 0.40 ohm. Six target lamps are included and three additional lamps are available as options in the Type SLAT51AF relay as shown on the internal connection diagram of Figure 2. Refer to the overall logic diagram of the particular scheme for target lamps provided. When TL32 is provided, its output will prevent the target lamps from turning on. A long pickup setting on this timer will permit all functions that operate to light their associated lamps. A short time setting will allow only those functions that operate initially to be indicated.

#### LOGIC CIRCUITS

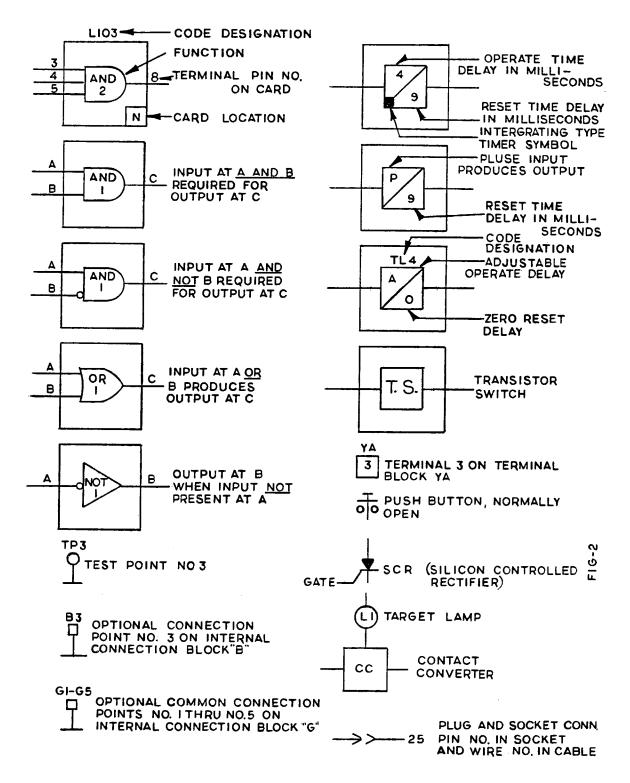

The functions of the Type SLAT51AF involve basic logic (AND, OR, and NOT) where the presence or absence of signals, rather than their magnitude, controls the operation. Signals are measured with respect to a reference bus accessible at TP1. In general, a signal below one volt DC represents an OFF or LOGIC ZERO condition; an ON or LOGIC ONE is represented by a signal of approximately plus 15 volt DC.

The symbols used on the internal connection diagram (Figure 2) are explained by the legend shown in Figure 4.

#### CALCULATION OF SETTINGS

There is one optional timer function in the SLAT51AF that requires field adjustment.

The 5-30/0 timer, TL32, enables the user to control the number of lamps that will light under certain fault conditions. With a short pickup setting (5-10 milliseconds) only lamp(s) associated with those units which first sensed the fault will light. Increased pickup settings will cause the lamps associated with all units that operate to light. The timer setting should not exceed the minimum breaker clearing time in order to avoid targets which may result from breaker unequal pole opening times.

#### CONSTRUCTION

The SLAT51AF relay is packaged in an enclosed metal case with hinged front cover and removable top cover. The outline and mounting dimensions of the case and the physical location of the components are shown in Figures 1 and 3, respectively.

The SLAT51AF relay contains printed circuit cards identified by a code number, such as A104, T115, L109; where A designates an auxiliary function, T designates a time-delay function, and L designates a logic function. The printed circuit cards plug in from the front of the unit. The sockets are marked with letter designations or "addresses" (D, E, F, etc.) which appear on the guide strips in front of each

socket, on the component location drawing, on the unit internal connection diagram, and on the printed circuit card. The test points (TP1, TP2, etc.) shown on the internal connection diagram are connected to instrument jacks on the test card in position T with TP1 at the top of the T card. TP1 is tied to reference; TP10 is tied to plus 15 volts DC through a 2.2K resistor. This resistor limits the current when TP10 is used to supply a logic signal to a card.

The SLAT51AF relay receives its inputs from the associated Type SLA relay. These units are interconnected by ten conductor shielded cables. The sockets for these cables are located on the rear panel of the unit. The SLAT51AF output functions are connected to 12-point terminal strips, which are also located on the rear of the unit.

A window is provided in the hinged cover of the relay to allow target lamps and the mechanical targets to be seen. Push buttons are also provided to reset the targets and lamps without opening the cover.

#### RECEIVING. HANDLING AND STORAGE

The SLAT51AF relay will normally be supplied as part of a static relay equipment, mounted in a rack or cabinet with other static relays and test equipment. Immediately upon receipt of a static relay equipment, it should be unpacked and examined for any damage sustained in transit. If damage resulting from rough handling is evident, file a damage claim at once with the transportation company and promptly notify the nearest General Electric Sales Office.

Reasonable care should be exercised in unpacking the equipment. If the equipment is not to be installed immediately, it should be stored indoors in a location that is free from moisture, dust, metallic chips, and severe atmospheric contaminants.

Just prior to final installation the shipping support bolt should be removed from each side of all relay units, to facilitate possible future unit removal for maintenance. These shipping support bolts are approximately eight inches back from the relay front panel. WARNING: STATIC RELAY EQUIPMENT, WHEN SUPPLIED IN SWING RACK CABINETS, SHOULD BE SECURELY ANCHORED TO THE FLOOR OR TO THE SHIPPING PALLET TO PREVENT THE EQUIPMENT FROM TIPPING OVER WHEN THE SWING RACK IS OPENED.

#### TEST INSTRUCTIONS

#### CAUTION

THE LOGIC SYSTEM SIDE OF THE DC POWER SUPPLY USED WITH MOD III STATIC RELAY EQUIP-MENT IS ISOLATED FROM GROUND. IT IS A DESIGN CHARACTERISTIC OF MOST ELECTRONIC INSTRUMENTS THAT ONE OF THE SIGNAL INPUT TERMINALS IS CONNECTED TO THE INSTRUMENT CHASSIS. IF THE INSTRUMENT USED TO TEST THE RELAY EQUIPMENT IS ISOLATED FROM GROUND, ITS CHASSIS MAY HAVE AN ELECTRICAL POTENTIAL WITH RESPECT TO GROUND. THE USE OF A TEST INSTRUMENT WITH A GROUNDED CHASSIS WILL NOT AFFECT THE TESTING OF THE EQUIPMENT. HOWEVER, A SECOND GROUND CONNECTION TO THE EQUIPMENT, SUCH AS A TEST

LEAD INADVERTENTLY DROPPING AGAINST THE RELAY CASE, MAY CAUSE DAMAGE TO THE LOGIC CIRCUITRY. NO EXTERNAL TEST EQUIPMENT SHOULD BE LEFT CONNECTED TO THE STATIC RELAYS WHEN THEY ARE IN PROTECTIVE SERVICE, SINCE TEST EQUIPMENT GROUNDING REDUCES THE EFFECTIVENESS OF THE ISOLATION PROVIDED.

IF THE SLAT51AF RELAY THAT IS TO BE TESTED IS INSTALLED IN AN EQUIPMENT WHICH HAS ALREADY BEEN CONNECTED TO THE POWER SYSTEM, DISCONNECT THE OUTPUTS TO THE SYSTEM DURING TEST.

## **GENERAL**

The SLAT51AF relay is supplied from the factory either mounted in a static relay equipment or as a separate unit associated with measuring relays, a Type SSA power supply, and some form of channel equipment. All relay units for a given terminal of static relaying equipment are tested together at the factory, and each unit will have the same summary number stamped on its nameplate.

In general, when a time range is indicated on the internal connections diagram, the timer has been factory set at a mid-range value. Timers should be set for the operating or reset times indicated on the associated overall logic diagram. Where a time range is indicated on the overall logic diagram, the timer should be set for the value recommended for that function in the descriptive write-up accompanying the overall logic diagram. Where a setting depends upon conditions encountered on a specific application, this is so stated and the factors influencing the choice of setting are described. The procedure for checking and setting the timers is described in a later section.

#### OPERATIONAL CHECKS

Operation of the SLAT51AF unit can be checked by observing the signals at the ten test points (TP1 to TP10) in the SLAT51AF, by observing the operation of the associated channel equipment; or by observing the output functions. The test points are located on the test card in position T, and are numbered 1 to 10 from top to bottom. TP1 is the reference bus for the logic circuit; TP10 is at plus 15 volts DC. The remaining points are located at various strategic points throughout the logic as shown on the internal connection diagram (Figure 2). Test point voltages can be monitored with a portable high impedance voltmeter, the voltmeter on the test panel of the associated equipment, or an oscilloscope.

#### TEST CARD ADAPTER

The test card adapter provides a convenient means of gaining access to any pin of a particular card. Detailed information on the use of the test adapter card is included in the printed circuit card instruction book, GEK-34158.

#### TIMER ADJUSTMENTS AND TESTS

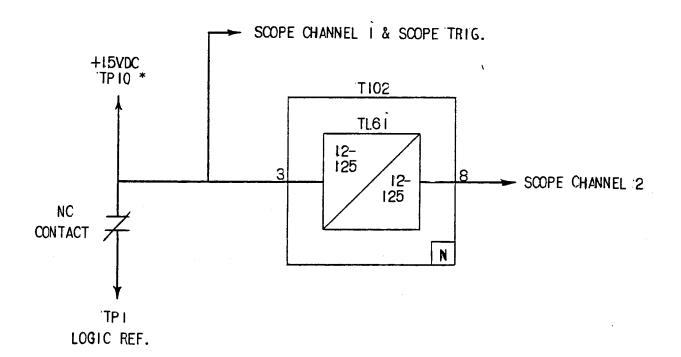

When the timer cards are to be adjusted or checked, an oscilloscope that can display two traces simultaneously, and that has a calibrated horizontal sweep, should be used.

In order to test the timer cards it is necessary to remove the card previous to the timer (see Table III) and to place the timer card in a card adapter. The card adapter allows access to the input and output of the timer if they are not brought out on test points. The timer test circuit is shown in Figure 5. Opening the normally closed contact causes the output to step up to plus 15 volts DC after the pickup delay of the timer. To increase the pickup time, turn the upper potentiometer on the timer card clockwise; to decrease the time, turn it counterclockwise. Closing the contact causes the timer output to drop out after the reset time-delay setting of the card. If the timer card is provided with a variable reset delay, it can be adjusted by the lower potentiometer on the timer card (clockwise increases reset time).

A timer tester card (0172C5151G-1) can be obtained to replace the test circuit of Figure 5. This card simply plugs into any card slot in the unit. The card contains two push button switches, two paralleled test plugs and a LED light. The test plugs connect to the input of the timer under test, and to trigger the timing device used. Pushing the green push button provides a bounceless switch to start the timer card, and turn the LED on. The red push button turns the test signal and the LED off.

# TABLE III

| TIMER UNDER<br>TEST | POSITION | REMOVE CARD<br>IN POSITION |

|---------------------|----------|----------------------------|

| TL33                | AR       | NONE **                    |

| TL32                | L        | AL                         |

\*\* Turn power supply switch on and off

#### TRIP CIRCUIT TESTS

The SCR trip circuits and series mechanical targets, or the contact trip circuits, may be checked by connecting a properly rated auxiliary lock-out relay, such as the Type HEA relay, in series with the trip circuit. If an auxiliary lock-out relay is not available, it can be replaced by a resistive load which limits the trip circuit current to three amperes. In most equipments the SCR trip circuit, or the contact trip circuit, can be gated by operating a test pushbutton in the associated units.

Prior to final installation, a check of the overall trip circuit should be made with the trip circuit outputs connected to trip the circuit breakers.

# OVERALL EQUIPMENT TESTS

After the SLAT51AF relay and the associated static relay units have been individually calibrated and tested for the desired settings, a series of overall operating circuit checks is advisable.

The elementary, overall logic and logic description for the specific job will be useful for determining the overall operation of the scheme.

Overall equipment tests can be performed by applying alternating current and voltages to the measuring units as specified in the instruction book for the measuring units and checking that proper outputs are obtained when the measuring units operate.

# **MAINTENANCE**

# PERIODIC TESTS

It should be sufficient to check the outputs produced at test points in the SLAT51AF when periodic calibration tests are made on the associated measuring units, for example, the phase and ground relays in a line relaying scheme. No separate periodic tests on the SLAT51AF itself should be required.

#### TROUBLESHOOTING

In any troubleshooting of equipment, it should first be established which unit is functioning incorrectly. The overall logic diagram supplied with the equipment shows the combined logic of the complete equipment and the various test points in each unit. By signal tracing, using the overall logic diagram and the various test points, it should be possible to quickly isolate the trouble.

A test adapter card is supplied with each static relay equipment to supplement the prewired test points on the test cards. Use of the adapter card is described in the printed circuit card instruction book, GEK-34158.

A dual-trace oscilloscope, is a valuable aid to detailed troubleshooting, since it can be used to determine phase shift, operate and reset times, as well as input and output levels. A portable dual-trace oscilloscope with a calibrated sweep and trigger facility is recommended.

#### SPARE PARTS

To minimize possible outage time, it is recommended that a complete maintenance program should include the stocking of a least one spare card of each type. It is possible to replace damaged or defective components on the printed circuit cards, but great care should be taken in soldering so as not to damage or bridge-over the printed circuit buses, or overheat the semiconductor components. The repaired area should be recovered with a suitable high-dielectric plastic coating to prevent possible breakdowns across the printed buses due to moisture and dust. The wiring diagrams for the cards in the SLAT51AF relay are included in the printed circuit card instruction book, GEK-34158.

Figure 1 (0227A2037-0) Outline and Mounting Dimensions for the Type SLAT51AF Relay

Figure 2 (0179C6384-0) Internal Connection Diagram for the Type SLAT51AF Relay

Figure 3 (0285A8128-0) Component Location Diagram for the Type SLAT51AF Relay

Figure 4 (0227A2047-1) Logic and Internal Connection Diagram Legend

\* THE 15VDC SIGNAL AT PIN 10 HAS A CURRENT LIMITING RESISTOR MOUNTED ON THE TEST CARD.

Figure 5 (0246A7987-0) Logic Timer Test Circuit

TYPICAL SCR TEST CIRCUIT FOR TYPE SLA RELAYS

Figure 6 (0208A2365-0) Typical Trip Circuit Test Connections

Figure 7 (0108B9610-0) Internal Connections for the SCR Trip and Isolator Subassemblies

# GENERAL ELECTRIC COMPANY POWER SYSTEMS MANAGEMENT BUSINESS DEPT. MALVERN, PA 19355