GEK-90672A

## PLS

## HYBRID SCHEME DUAL FSK CHANNELS PHASE IDENTIFIED LOGIC FOR UNCOMPENSATED LINES

**GE Power Management**

These instructions do not purport to cover all details or variations in equipment nor provide for every possible contingency to be met in connection with installation, operation, or maintenance. Should further information be desired or should particular problems arise which are not covered sufficiently for the purchaser's purpose, the matter should be referred to the General Electric Company.

To the extent required the products described herein meet applicable ANSI, IEEE, and NEMA standards; but no such assurance is given with respect to local codes and ordinances because they vary greatly.

2

3

4

5

6

7

8

## SCHEME DESCRIPTION CALCULATION OF SETTINGS HARDWARE DESCRIPTION MODULES ACCEPTANCE TESTS

**PERIODIC TESTING**

SERVICING

**SPECIFICATIONS**

**CONTINUOUS MONITOR**

## SOFTWARE

9

## TABLE OF CONTENTS

| INTRODUCTION (GEA-11798)                                     | IN-1            |

|--------------------------------------------------------------|-----------------|

| SCHEME DESCRIPTION                                           | 1-1             |

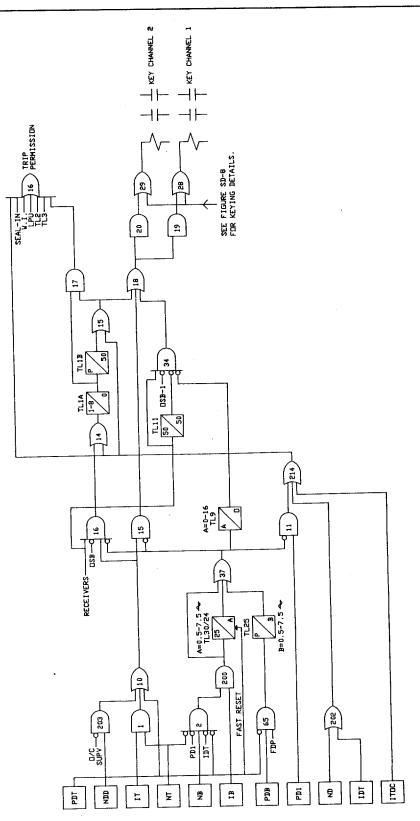

| Directional Comparison Logic                                 |                 |

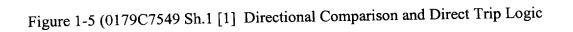

| Weak Infeed/Repeat Keying/Line Pickup Trip/Out-Of-Step Logic | 1-3             |

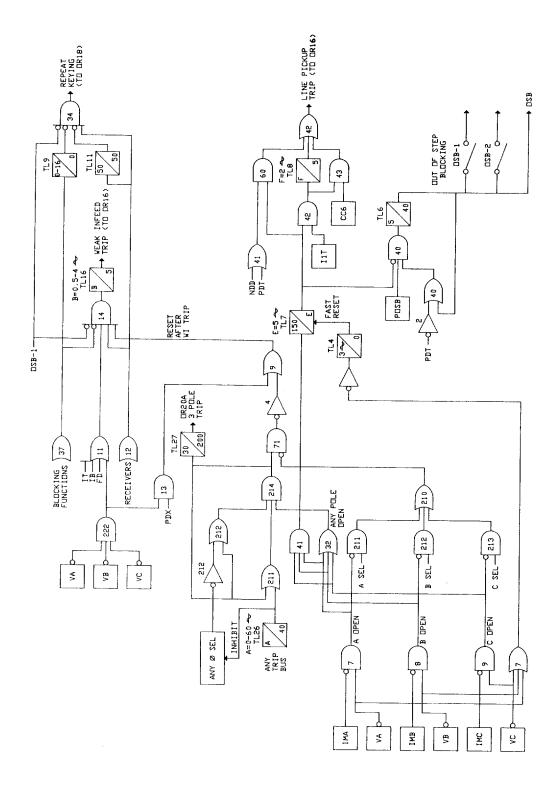

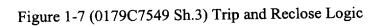

| Trip And Reclose Logic                                       | 1-4             |

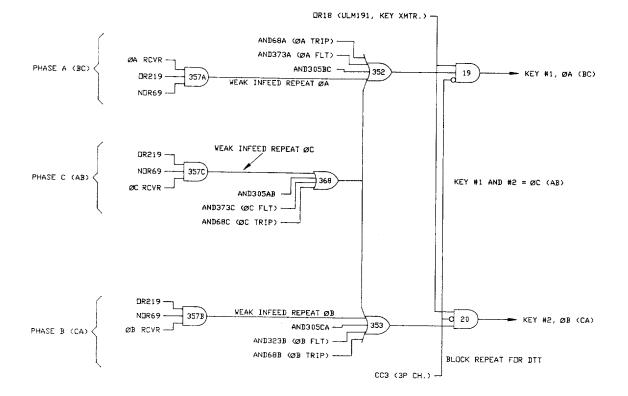

| Channel Logic                                                | 1-6             |

| Trin Calastian Lagia                                         | 1-0<br>1_7      |

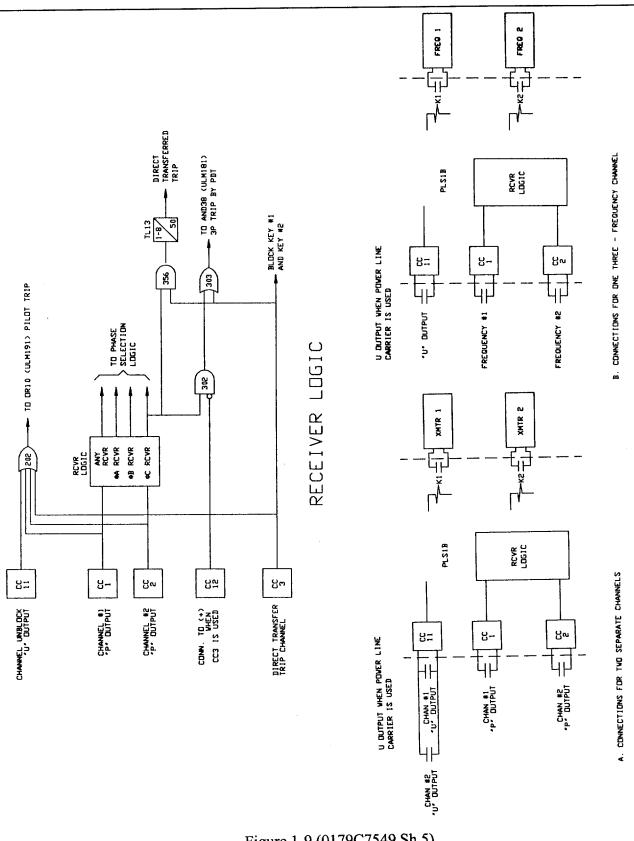

| Trip Selection Logic                                         | ,               |

| CALCULATION OF SETTINGS                                      | 2-1             |

| PD1 and ND - Zone 1 Direct Tripping Functions                | 2-1             |

| Settings                                                     | 2-1             |

| Z1                                                           |                 |

| PD1 Bias                                                     |                 |

| ND Bias                                                      | 2-1             |

| Negative Sequence Distance Units, N2 and N3                  | 2-2             |

| Setting Example                                              | 2-2             |

| Reach Setting, Z1                                            |                 |

| PD1 and ND Bias                                              | 2-2             |

| Positive Sequence Overreaching Distance Function, PDT        | 2-3             |

| Positive Sequence Overreaching Distance Function, 1 D 1      | ·····2.5<br>7_4 |

| Settings<br>ZT - Forward Reach                               | ·····2-4<br>2 1 |

| $\Sigma_1$ - Forward Reach                                   | ·····2-4        |

| Offset - PDT forward offset                                  |                 |

| PDT TC - PDT time constant                                   |                 |

| Setting Example                                              |                 |

| Positive Sequence Distance Blocking Function, PDB            |                 |

| Settings                                                     | 2-6             |

| PDB - Reach                                                  | 2-6             |

| PDB TC - PDB Time Constant                                   | 2-6             |

| PDB Setting Example                                          | 2-7             |

| Pos. Sea. Out-Of-Step Dist. Function, POSB                   | 2-7             |

| Pos. Seq. Auxiliary Distance Function, PDX                   | 2-7             |

| ZR1 - System Impedance Angle                                 | 2-8             |

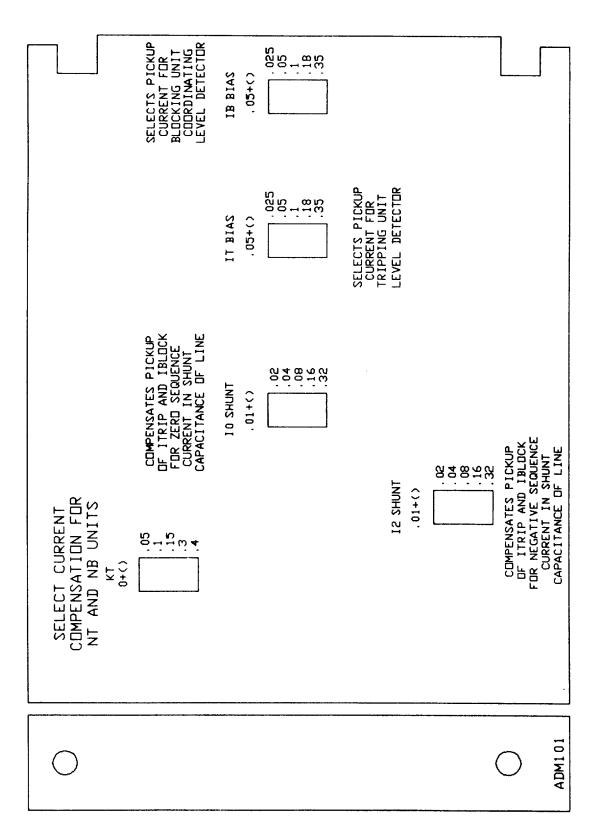

| Negative Sequence Dir. Function, NT and NB                   | 2-9             |

| Settings                                                     | 2-9             |

| KT                                                           | 2-9             |

| VA2                                                          |                 |

| Setting Example                                              | 2-9             |

| Juliig Example                                               | 2-9             |

| IT, IB, I2 Shunt AND I0 Shunt                                | 2_10            |

| Settings                                                     | 2-10            |

| IB Setting (IB Bias)                                         | 2-10            |

| IT Setting (IT Bias)                                         | 2-10            |

| I2 Shunt setting (I2 SHUNT)                                  | 2-11            |

| IO Shunt setting (IO SHUNT)                                  |                 |

| Setting Example                                              | 2-11            |

| IT Bias                                                      | 2-12            |

| I2 Shunt                                                     | 2-12            |

| IO Shunt                                                     | 2-12            |

| IDT - Overcurrent Direct Tripping Function                   | 2-13            |

|                                                              |                 |

|        | Settings                                                           | .2-             | 14            |

|--------|--------------------------------------------------------------------|-----------------|---------------|

|        | Setting Example<br>Pos. Seq. Overcurrent Line Pickup Function, I1T | 2-              | 14            |

| ]      | Pos. Seq. Overcurrent Line Pickup Function, 11T                    | 2_              | 16            |

|        | Setting Example<br>ITOC - Time Overcurrent Function                | . <u>ມ</u><br>ົ | 16            |

| 1      | ITOC - Time Overcurrent Function                                   | .2-             | 10            |

|        |                                                                    | .2-             | 1/            |

|        | TOC PU                                                             | .2-             | 18            |

|        | TOC K1                                                             | .2-             | 18            |

|        | TOC DIR                                                            | .2-             | 18            |

|        | TD                                                                 | .2-             | 18            |

| l      | IMA, IMB, IMC - Phase Current Functions                            | .2-             | 18            |

| -      | 310 - Zero Sequence Current Function                               | .2-             | 18            |

| (      | OSB1, OSB2 - Out-Of-Step Blocking                                  | 2-              | 19            |

|        | OSB1                                                               | $\tilde{2}_{-}$ | 10            |

|        | OSB2                                                               | .2-<br>ົ        | 10            |

| 1      | Logic Timers                                                       | . <u> </u>      | 17            |

|        |                                                                    | .2-             | 19            |

|        | Zone 2                                                             | .2-             | 19            |

|        | Zone 3                                                             | .2-             | 19            |

|        | Weak Infeed                                                        | .2-2            | 20            |

|        | <u>TL1</u>                                                         | .2-2            | 20            |

|        | TL9                                                                | .2-2            | 20            |

|        | TL24                                                               | .2-2            | 20            |

|        | TL25                                                               | 2-              | 20            |

|        | TL26                                                               |                 |               |

| -      | TL13, TL22- Transfer Trip Timers                                   | $\frac{2}{2}$   | 20            |

| Ī      | Reclosing Control                                                  | <br>ົ່າ         | 20<br>71      |

| -      | Settings                                                           | 2-1             | 21<br>72      |

| (      | Contact Convertere                                                 | 2-1             | 23            |

|        | Contact Converters.                                                | 2-2             | 23            |

| ,      | Channel Keying Outputs                                             | 2-2             | 24            |

|        | Key Xmtr 1 (K1)                                                    | 2-2             | 24            |

|        | Key Xmtr 2 (K2)                                                    | 2-2             | 24            |

|        |                                                                    |                 |               |

| HARDW  | ARE DESCRIPTION                                                    | 3-1             | 1             |

| (      | Case Assembly                                                      | 3-              | Ī             |

|        | Construction                                                       | 3_1             | ì             |

|        | Electrical Connections and Internal Wiring                         | 3_1             | 1             |

|        | Identification                                                     | 2 1             | ו<br>ו        |

| T      | Printed Circuit Board Modules                                      | 2-1             | 1<br>7        |

| 1      | Resic Construction                                                 | .⊃-∡<br>^ ⁄     | <u>ב</u><br>ר |

|        | Basic Construction                                                 | 3-2             | 2             |

| т      | Identification                                                     | 3-4             | 2             |

| ł      | Receiving, Handling And Storage                                    | 3-2             | 2             |

| 1      | nstallation                                                        | 3-2             | 2             |

|        | Environment                                                        | 3-2             | 2             |

|        | Mounting                                                           | 3-2             | 2             |

|        | External Connections                                               | 3-3             | 3             |

| S      | Surge Ground Connections                                           | 3-7             | 3             |

| Ι      | Directional Check                                                  | 3_6             | โ             |

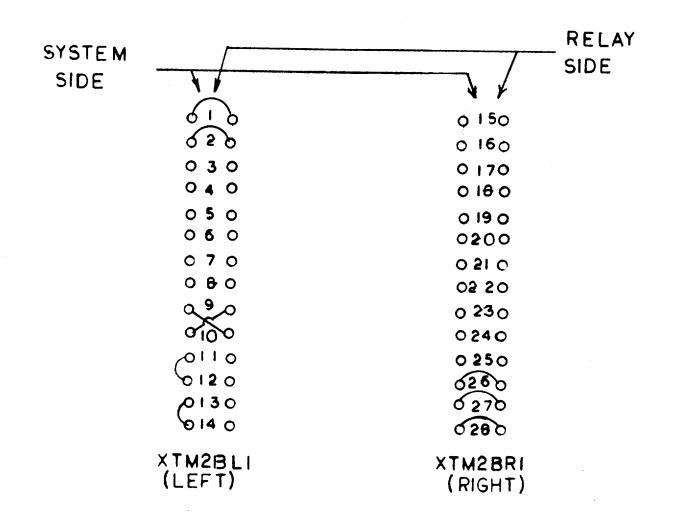

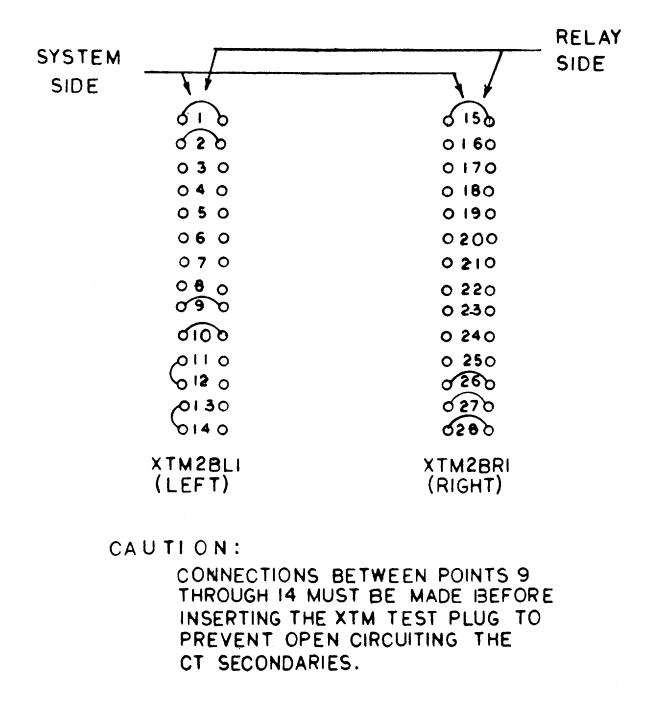

| ,      | XTM Test Plugs                                                     | 3.4             | ś             |

| ,<br>T | Ferminal Designation                                               | 24              | ,<br>,        |

| ,<br>T | XTM Test Circuit Connections                                       | 3-C             | י<br>ד        |

| ע<br>ר | Fest Ding Insertion                                                | 3-1             | 7             |

|        | Fest Plug Insertion                                                | 5-1             | (             |

| (      | Card Extender                                                      | 3-8             | 5             |

| MODULE DESCRIPTION                      | 4-1        |

|-----------------------------------------|------------|

| ADM10                                   | 4-1        |

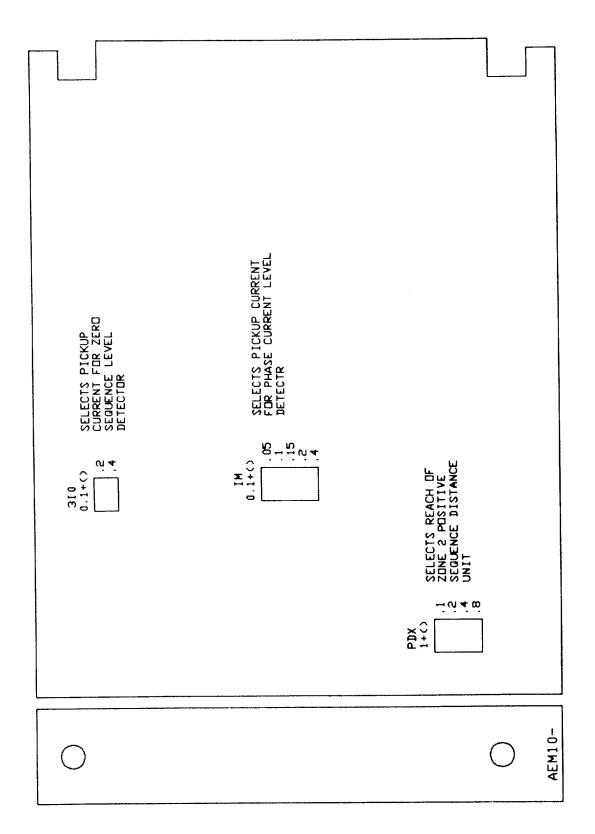

| AEM10                                   | 4-2        |

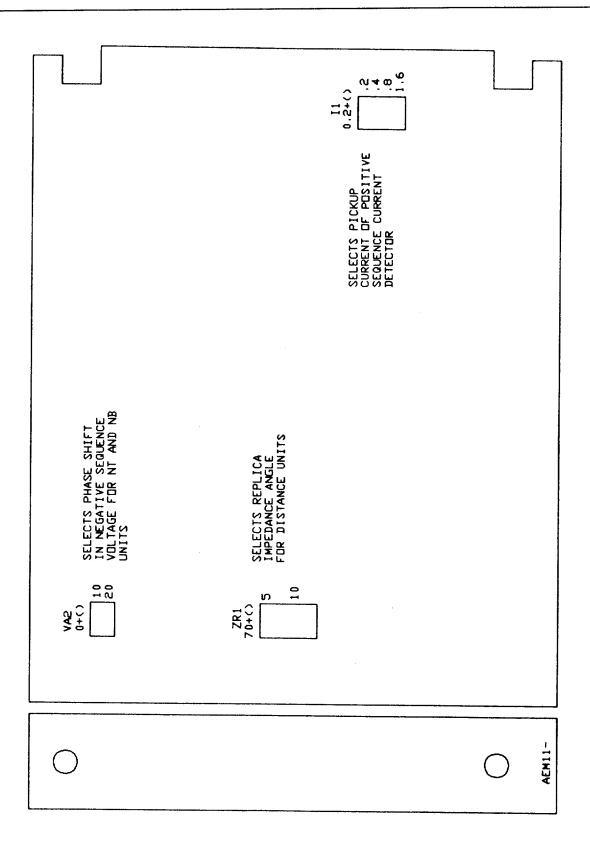

| AEM11                                   | 4-2        |

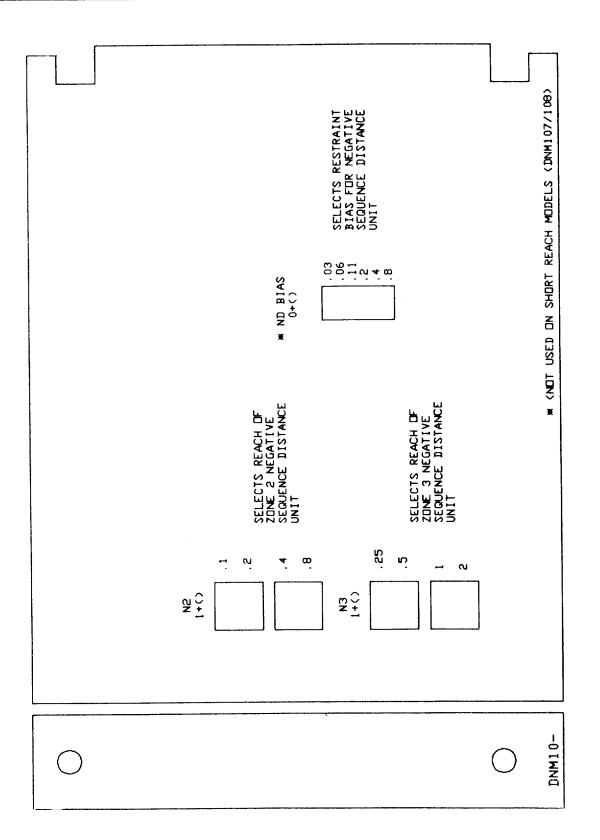

| DNM10                                   | 4-2        |

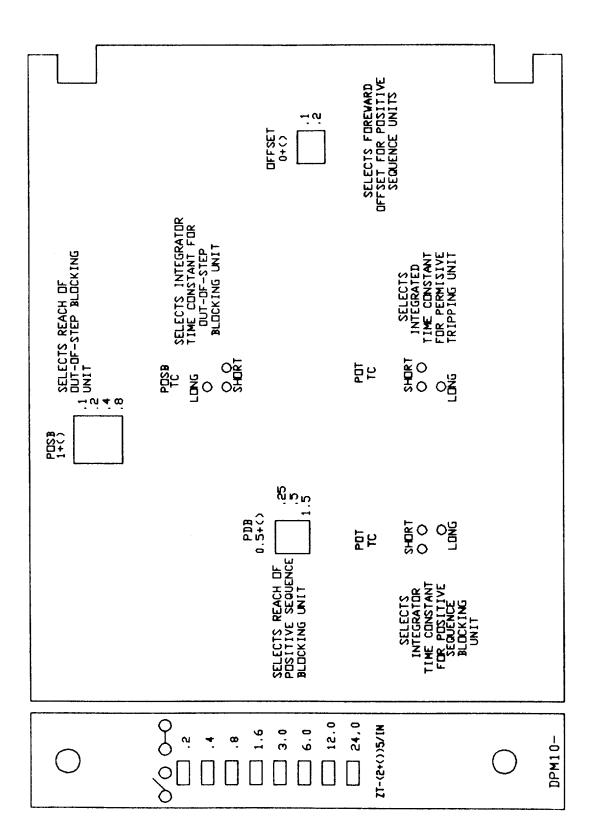

| DPM10                                   | 4-3        |

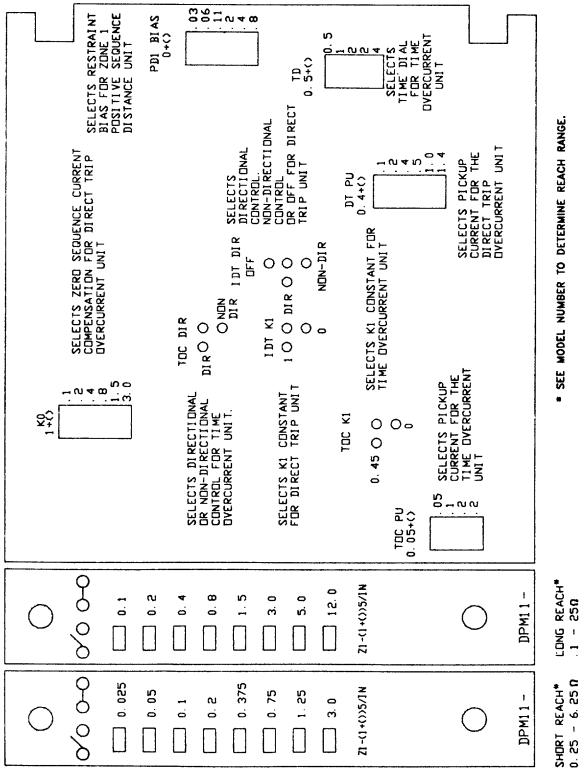

| DPM11                                   | 4-4        |

| DSM20                                   | 4-5        |

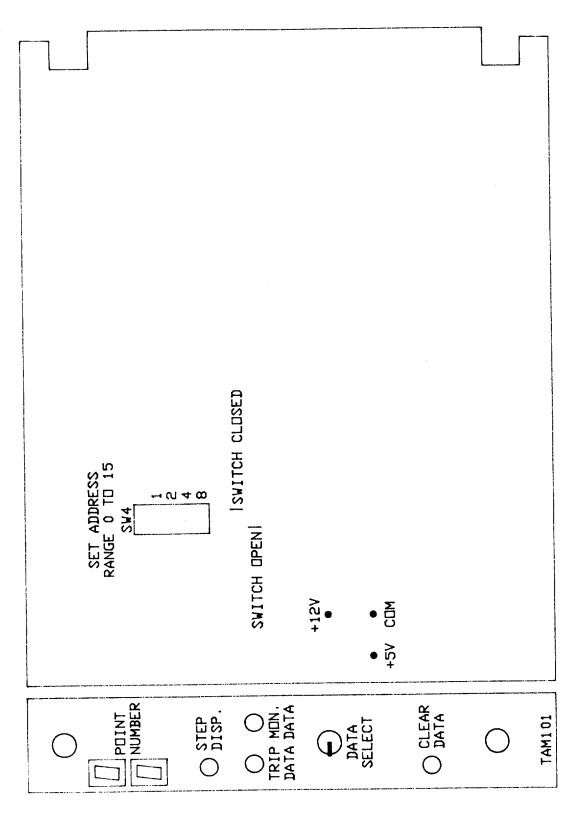

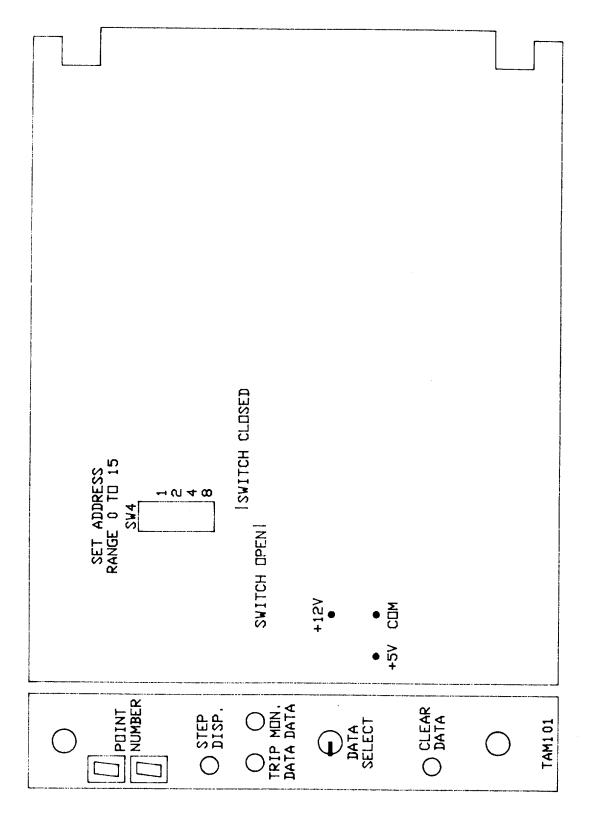

| TAM101                                  | 4-5        |

| UILM15                                  | 4-5        |

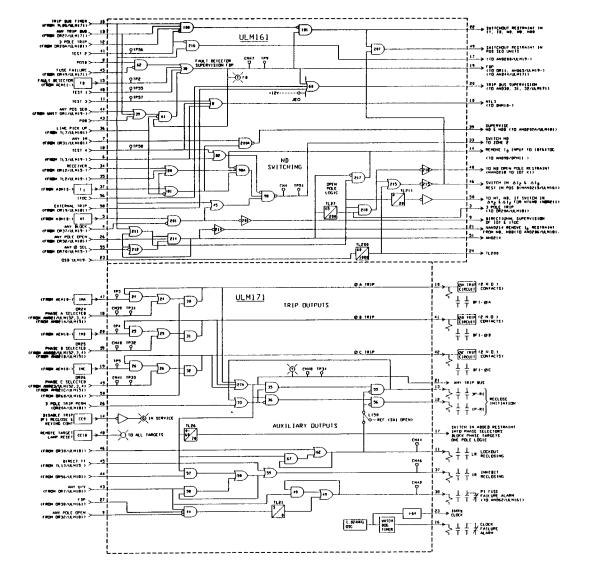

| UT_M161                                 | 4-6        |

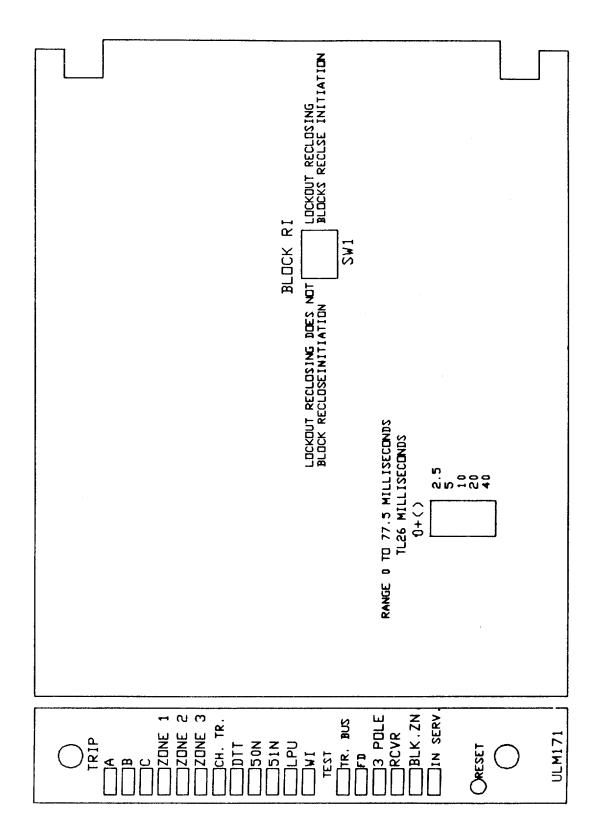

| UT.M171                                 | 4-6        |

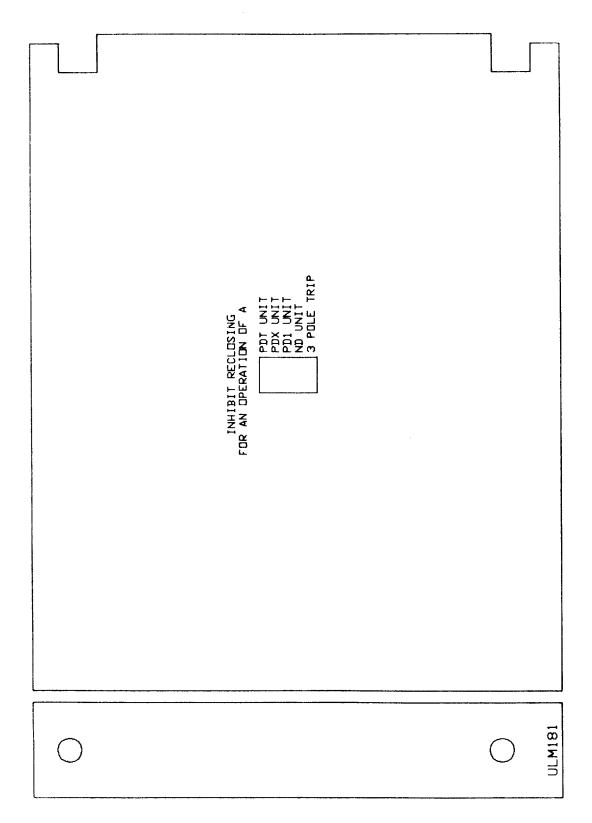

| ULM181                                  | 4-7        |

| <u>ИЛ.М19-</u>                          | 4-7        |

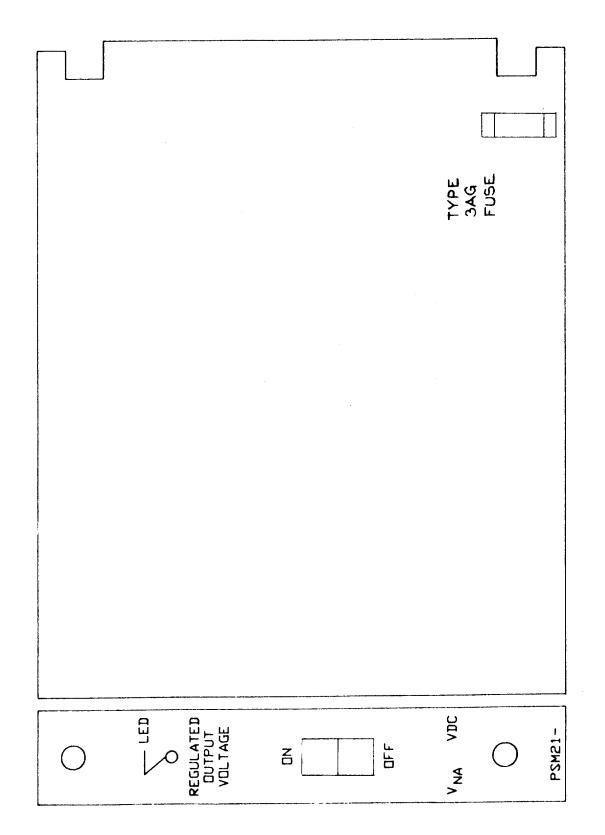

| PSM21                                   | 4-8        |

|                                         |            |

| ACCEPTANCE TESTS                        | 5-1        |

| Acceptance Tests                        |            |

| Required Settings                       |            |

| Test Equipment                          |            |

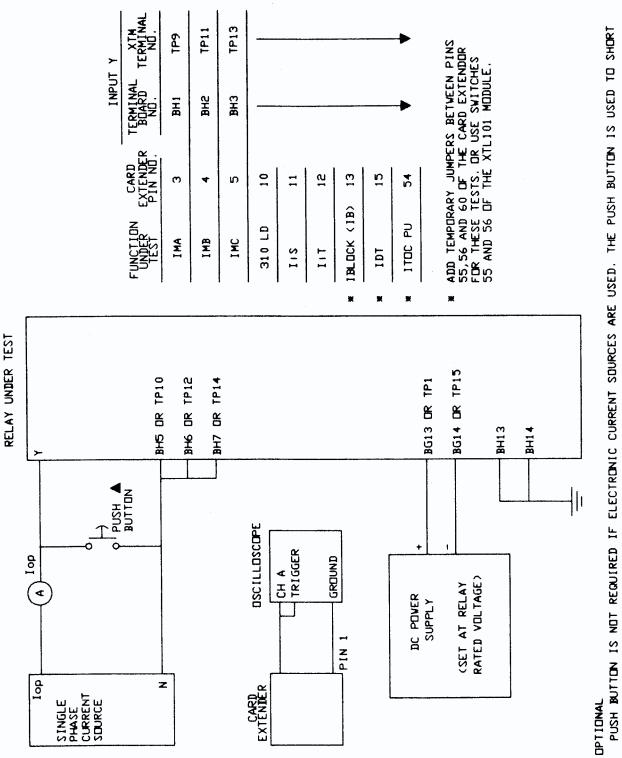

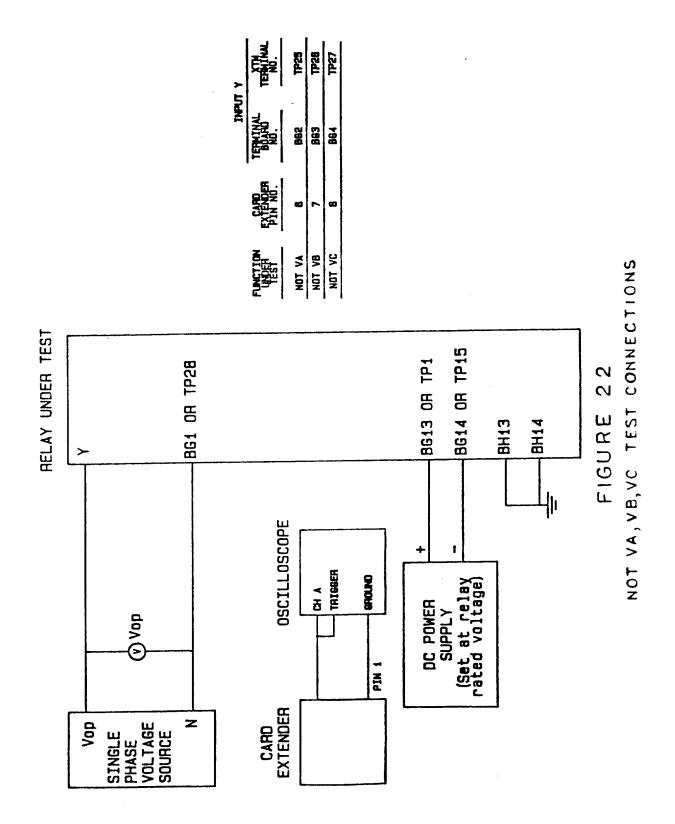

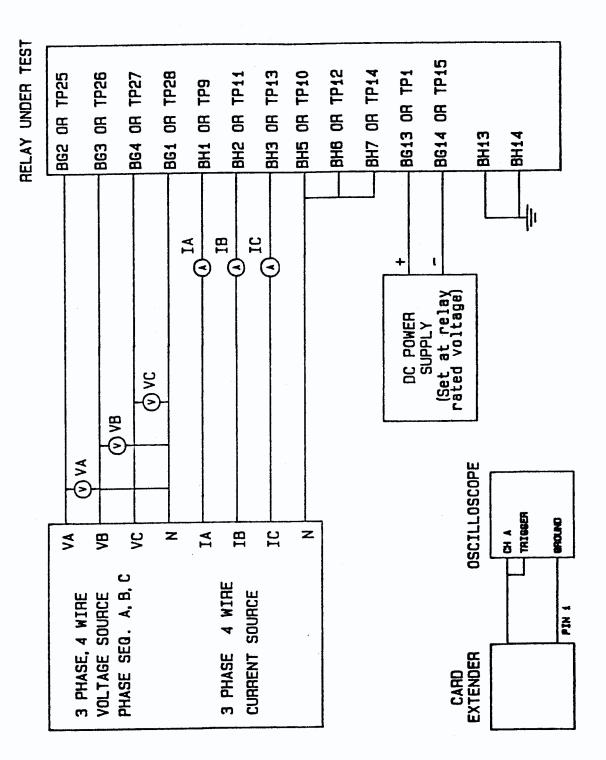

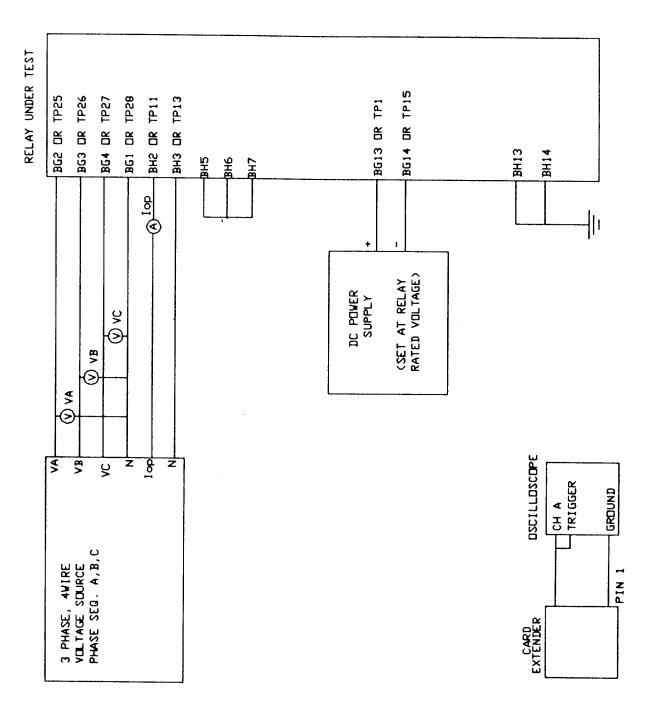

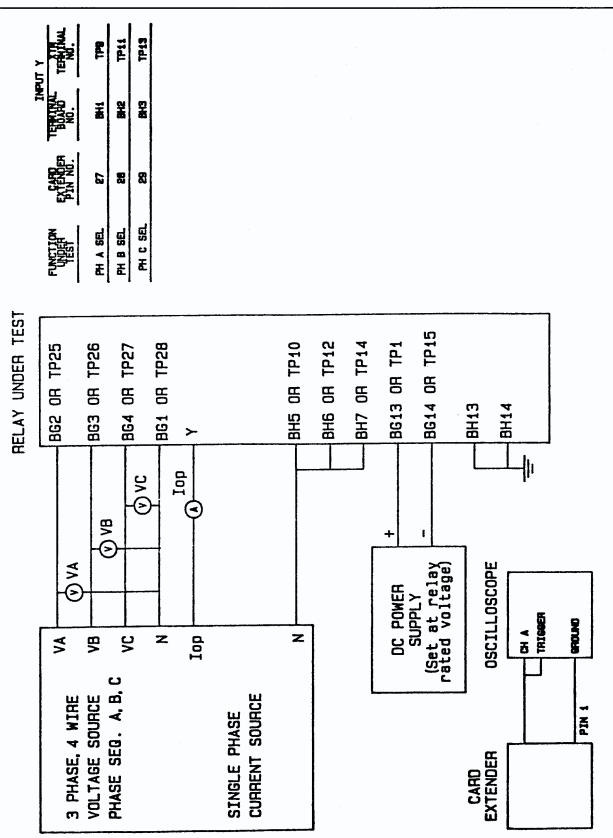

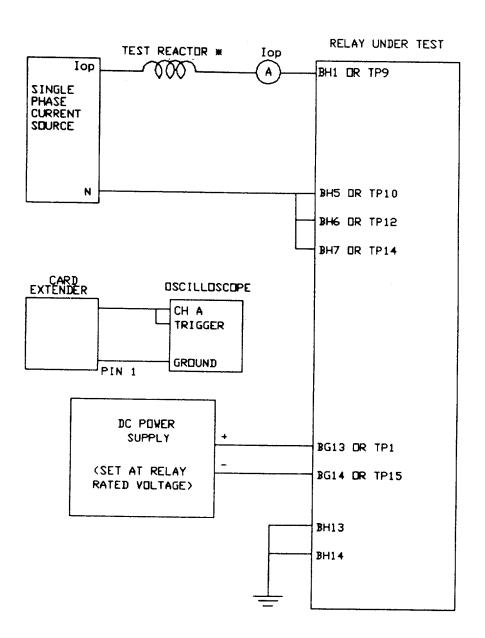

| Test Connections                        |            |

| Initial Relay Settings                  |            |

| General Instructions                    | 5-3        |

| Level Detector Tests                    |            |

| Positive Sequence Distance Tests        |            |

| Long Reach Scheme Setup (PD1)           |            |

| Short Reach Scheme Setup (PD1)          |            |

| PD1 Reach                               |            |

| PDX Reach                               |            |

| PDT Reach                               |            |

| POSB Reach                              |            |

| PDB Reach                               |            |

| Negative Sequence Distance Tests        |            |

| ND                                      |            |

| ND Zone 2 Reach                         |            |

| ND Zone 3 Reach                         |            |

| NDD                                     |            |

| NDD Zone 2 Reach                        |            |

| NDD Zone 3 Reach                        |            |

| Negative Sequence Directional Tests     |            |

| Phase Selectors                         |            |

| Dielectric Tests                        |            |

|                                         | 6-1        |

| PERIODIC TESTING                        | 0-1<br>6_1 |

| Testing The PLS With Different Settings |            |

| Tolerance                               | 5-1<br>6_1 |

| Current Level Detectors                 | 0 1<br>6_1 |

| IMA, IMB, IMC                           |            |

| 310<br>11T                              | 0 2<br>6_7 |

| 11 T<br>IB                              |            |

| IB<br>IT                                |            |

| 11                                      |            |

-3-

|        | Fault Detector Pickup6-4                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Directional Tests                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|        | ITOC (Non-directional)                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | ITOC (Directional)                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | IDT (Non-directional)6-5                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|        | IDT (Directional)                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|        | Positive-Sequence Distance Units                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | PD1                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | PDT6-7                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | PDB                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | POSB                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        | PDX                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | Negative-Sequence Distance Units                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        | NDD                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | NDD Zone 2 Reach                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | NDD Zone 3 Reach                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | ND                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | ND Zone 2 Reach                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        | ND Zone 3 Reach                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        | Negative Sequence Directional Tests                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | NT Unit6-13                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|        | NB Unit6-13                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|        | Phase Selectors                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SERVI  | CING                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        | Spares                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | Spares                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | Spares    7-1      Without The Continuous Monitor Module    7-1      With The Continuous Monitor Module    7-1                                                                                                                                                                                                                                                                                                                                           |

|        | Spares                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2                                                                                                                                                                                                                                                                                                                                             |

| SPECII | Spares    7-1      Without The Continuous Monitor Module    7-1      With The Continuous Monitor Module    7-1                                                                                                                                                                                                                                                                                                                                           |

| SPECII | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2                                                                                                                                                                                                                                                                                                                                             |

| SPECIE | Spares       7-1         Without The Continuous Monitor Module       7-1         With The Continuous Monitor Module       7-1         Power Supply Module       7-2         ICATIONS       8-1                                                                                                                                                                                                                                                           |

| SPECII | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1                                                                                                                                                                                                                                                                                                              |

| SPECII | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2                                                                                                                                                                                                                                                                                               |

| SPECII | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3                                                                                                                                                                                                                                                            |

| SPECII | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Accuracy8-3                                                                                                                                                                                                                                                 |

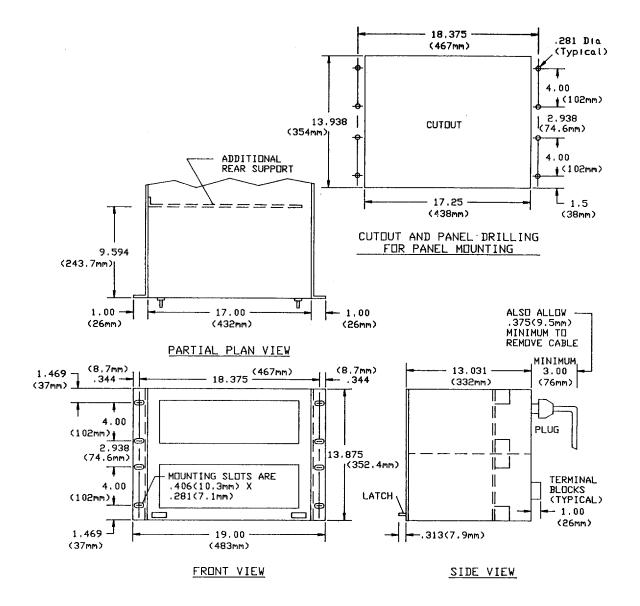

| SPECII | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Accuracy8-3Dimensions8-3                                                                                                                                                                                                                                    |

| SPECII | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Accuracy8-3                                                                                                                                                                                                                                                 |

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3                                                                                                                                                                                                                                      |

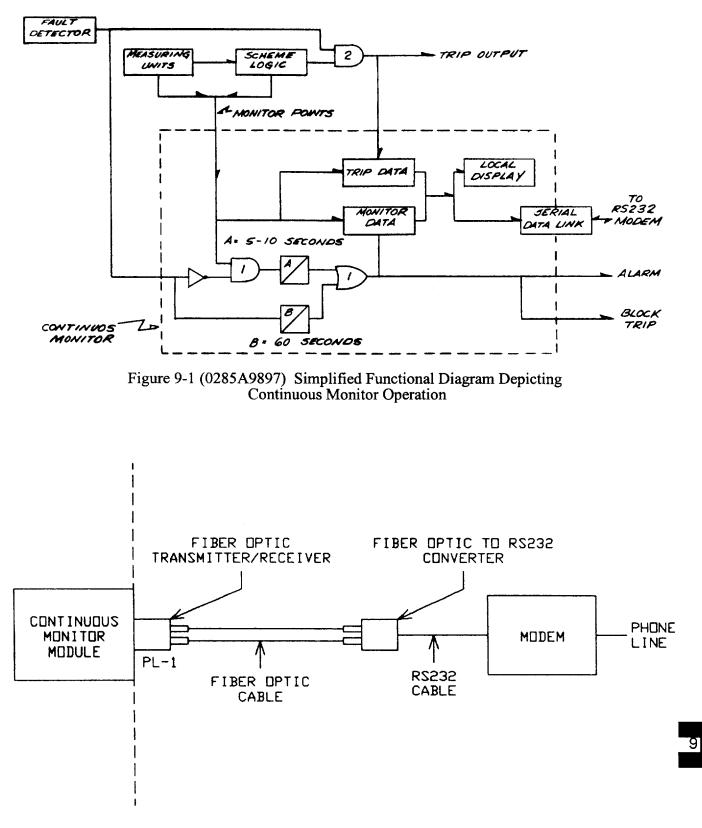

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1                                                                                                                                                                                                                      |

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1                                                                                                                                                                                                    |

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1Additional Function9-1                                                                                                                                                                              |

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1Additional Function9-1Access Of Stored Data9-2                                                                                                                                                      |

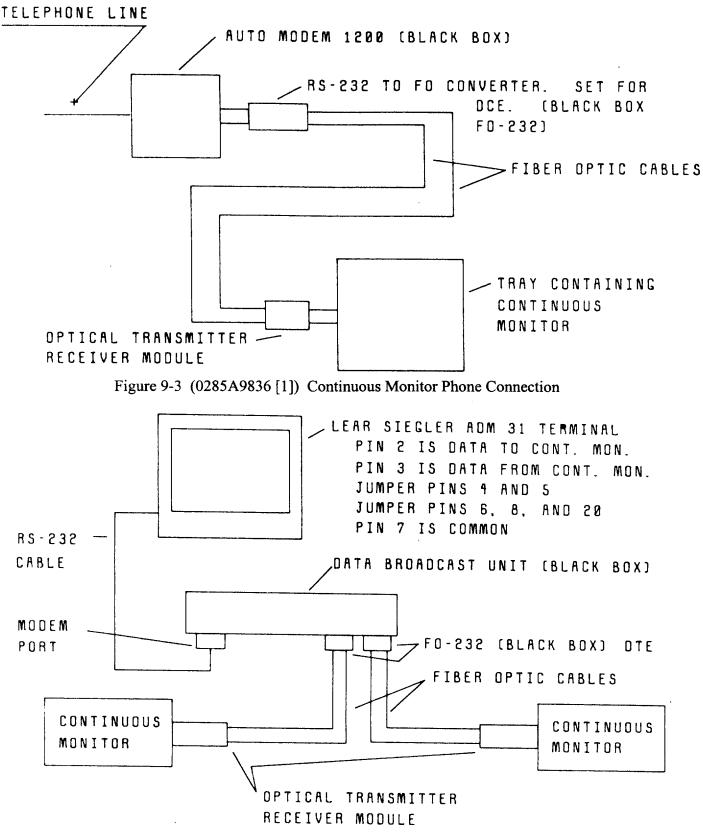

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1Additional Function9-1Access Of Stored Data9-2Local Access9-2                                                                                                                                       |

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1Additional Function9-1Access Of Stored Data9-2Local Access9-2Remote Access9-2Remote Access9-2                                                                                                       |

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Accuracy8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1Additional Function9-1Access Of Stored Data9-2Local Access9-2Remote Access9-2Clearing the Stored Data9-4                                                                                 |

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1Additional Function9-1Access Of Stored Data9-2Local Access9-2Clearing the Stored Data9-4Modes Of Operation9-4                                                                                       |

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Accuracy8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1Additional Function9-1Access Of Stored Data9-2Local Access9-2Clearing the Stored Data9-4Modes Of Operation9-4Local-Display Mode9-5                                                       |

|        | Spares.7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module.7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data.8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1Additional Function9-1Access Of Stored Data9-2Local Access9-2Clearing the Stored Data9-4Modes Of Operation9-4Local-Display Mode9-5Serial-Data-Link-Access Mode9-5                                |

|        | Spares7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1Additional Function9-1Access Of Stored Data9-2Local Access9-2Clearing the Stored Data9-4Modes Of Operation9-4Local-Display Mode9-5Serial-Data-Link-Access Mode.9-5Continuous Monitor Adjustments9-5 |

|        | Spares.7-1Without The Continuous Monitor Module7-1With The Continuous Monitor Module7-1Power Supply Module.7-2ICATIONS8-1Ratings8-1Burdens8-1Contact Data.8-2Replica Impedance Angle Settings8-3Dimensions8-3Weight8-3NUOUS MONITOR9-1Basic Operation9-1Additional Function9-1Access Of Stored Data9-2Local Access9-2Clearing the Stored Data9-4Modes Of Operation9-4Local-Display Mode9-5Serial-Data-Link-Access Mode9-5                                |

.

| SOFTWARE            |  |

|---------------------|--|

| Running the Program |  |

| ŠET PLŠ             |  |

| CONTMON             |  |

## **LIST OF FIGURES**

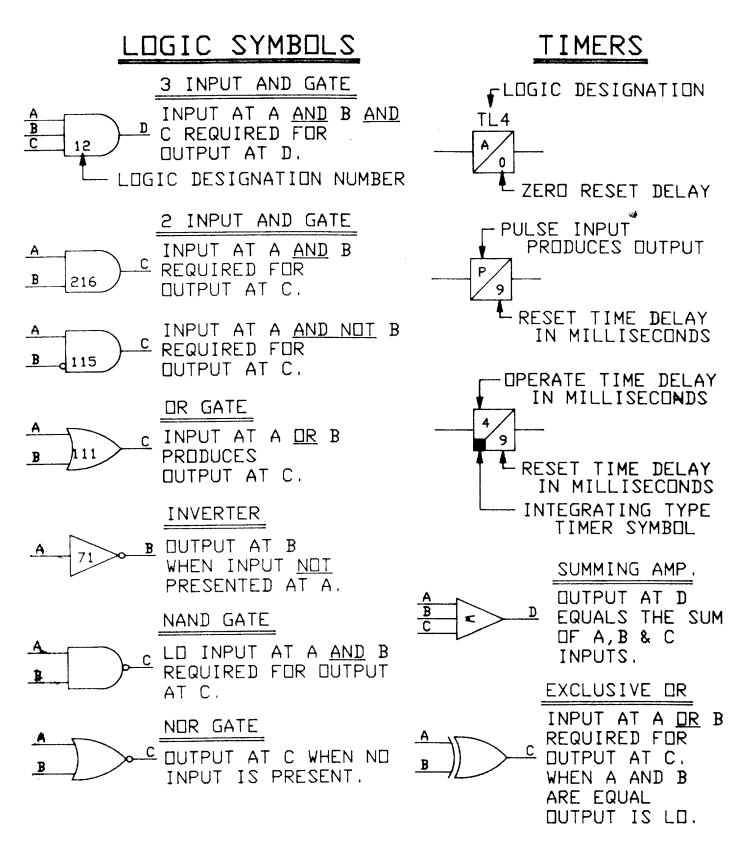

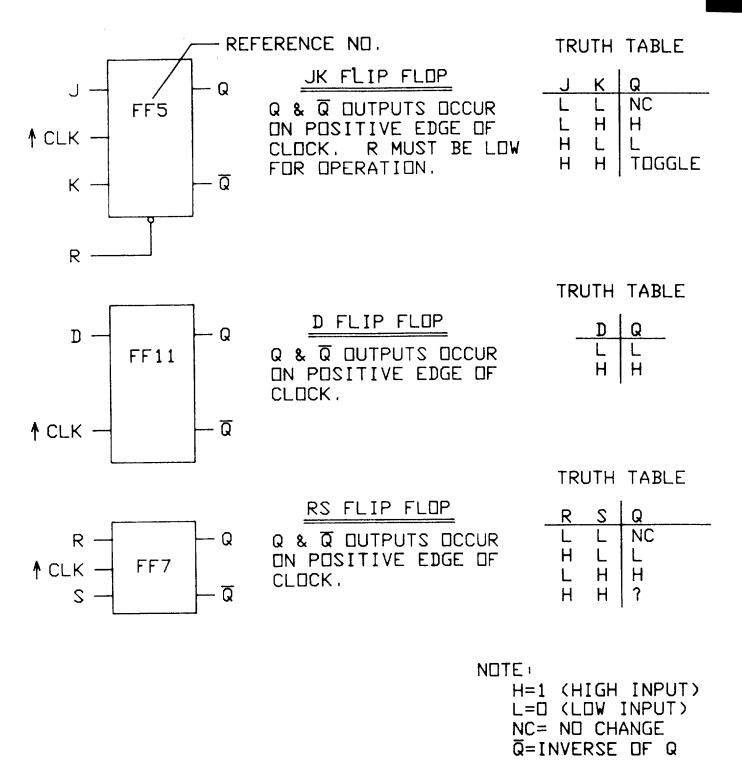

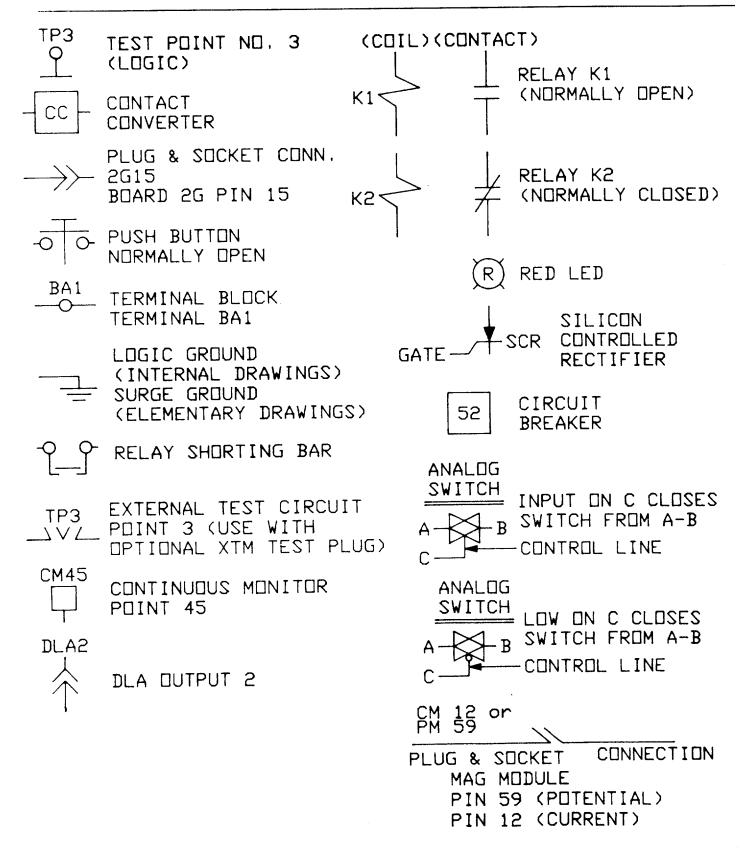

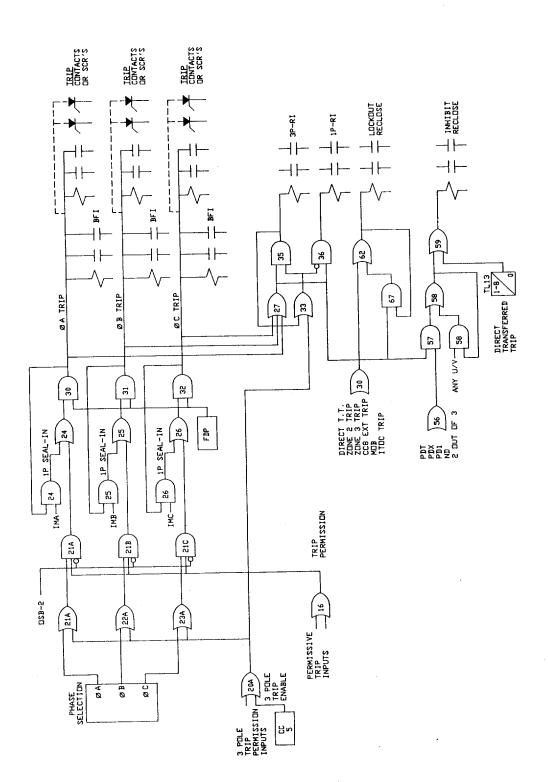

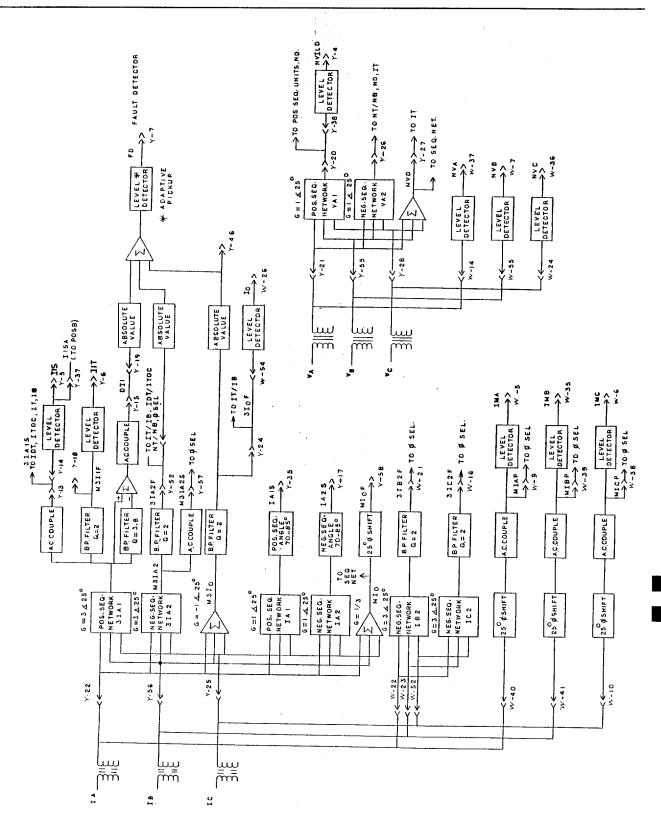

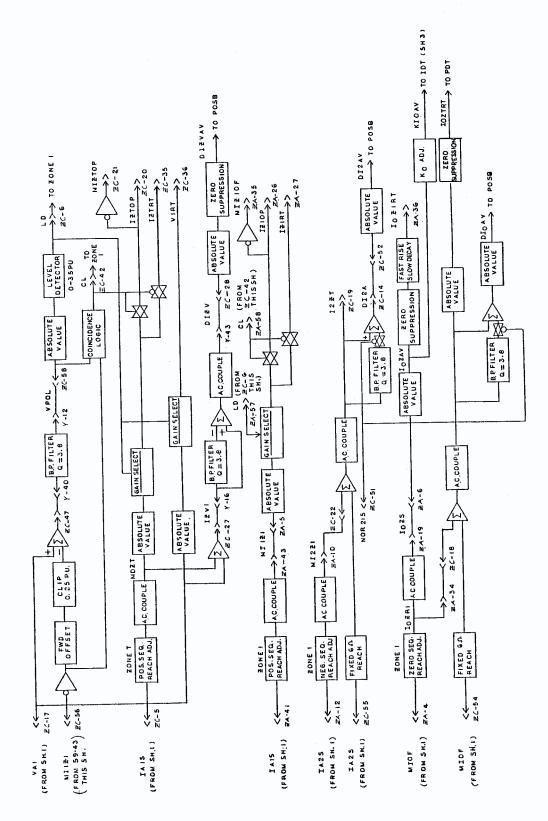

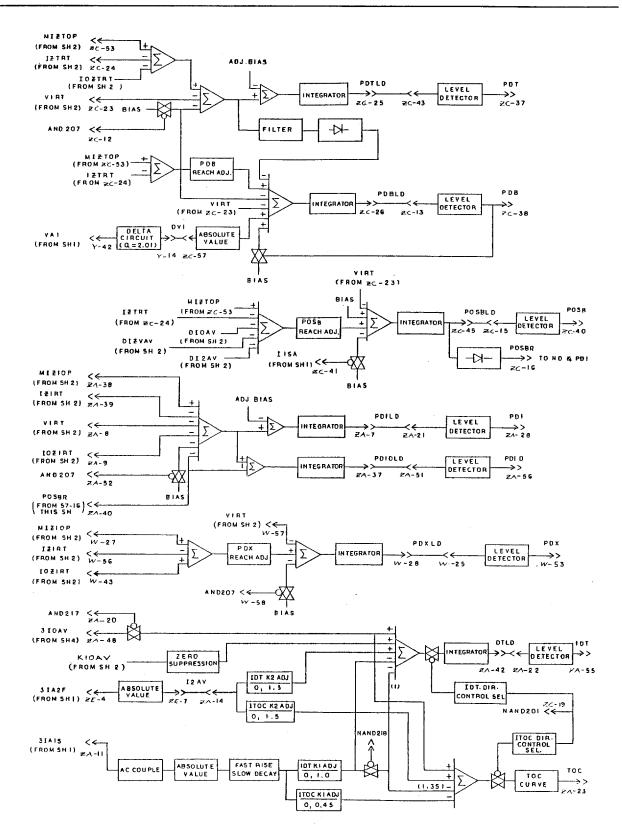

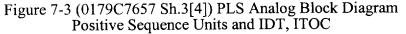

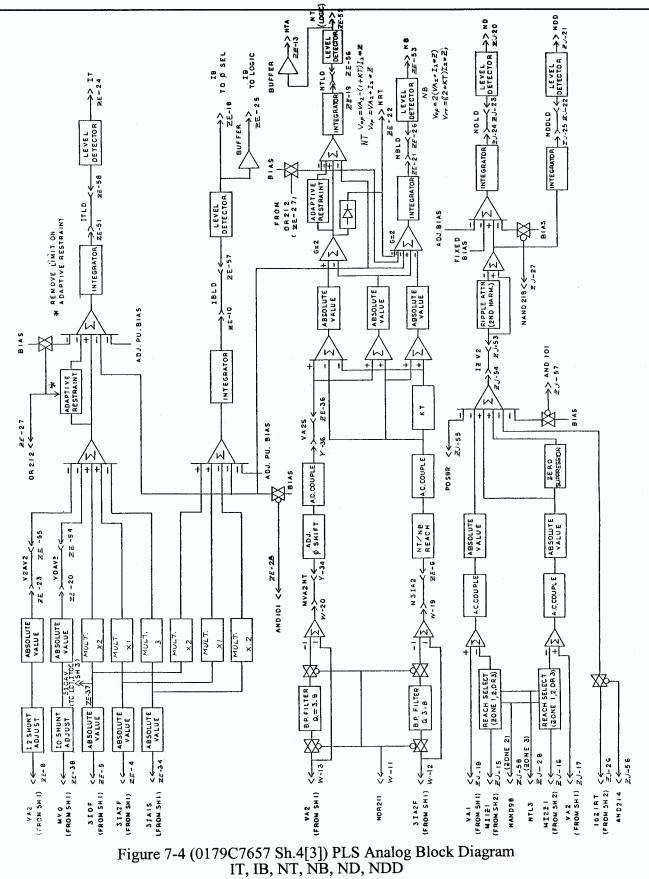

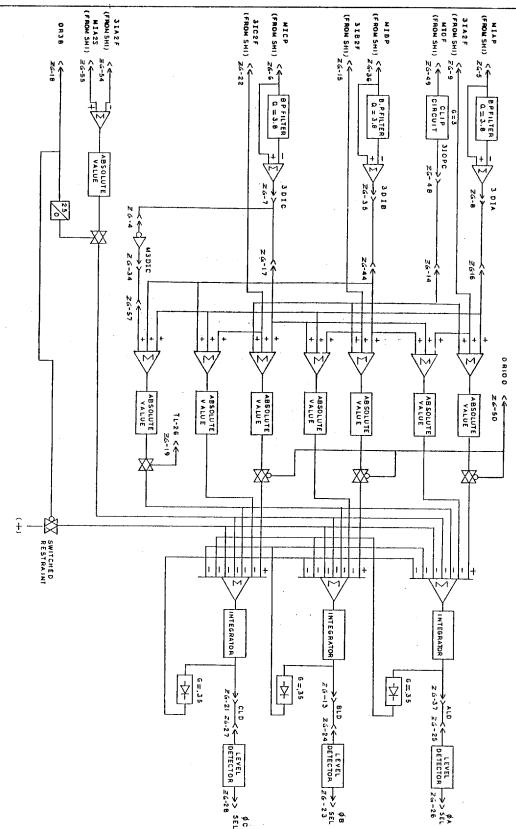

| Figure 1-2Logic and Internal Diagram Legend1-10Figure 1-3Logic Diagram1-13Figure 1-4Elementary Diagram1-16Figure 1-5Dir. Comparison/Direct Trip Logic1-17Figure 1-6Weak Infeed/Repeat Key/LinePU/Out-of-Step Logic1-18Figure 1-7Trip and Reclose Logic1-19Figure 1-8Keying Circuits for Phase-Identified Channels1-20Figure 1-9Receiver Logic and Connections1-21Figure 1-10Phase-A Trip Selection1-23Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-4Figure 2-4PDX Function2-25Figure 2-5Connections for Communication Channels2-25Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Front View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-14Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-10ULM15-4-18Figure 4-10ULM15-4-18 | Figure 1-1  | MOD 10 <sup>TM</sup> Mnemonic Legend                 | 1-9                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------|------------------------------|

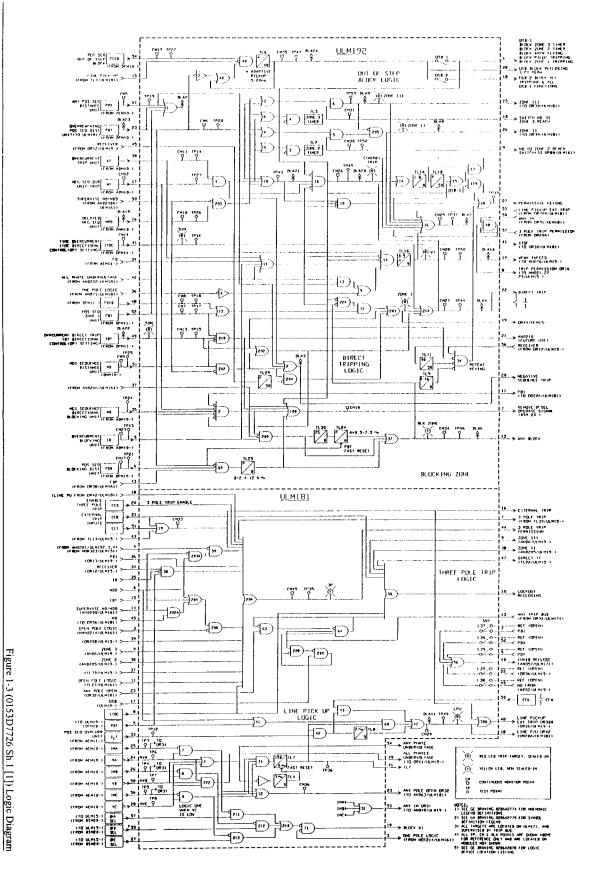

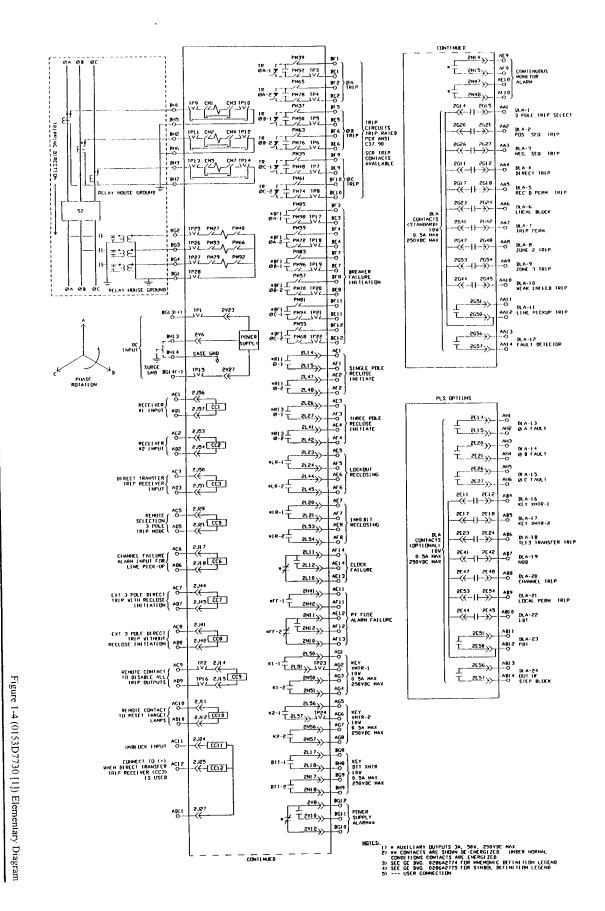

| Figure 1-3Logic Diagram1-13Figure 1-4Elementary Diagram1-16Figure 1-5Dir. Comparison/Direct Trip Logic1-17Figure 1-6Weak Infeed/Repeat Key/LinePU/Out-of-Step Logic1-18Figure 1-7Trip and Reclose Logic1-19Figure 1-8Keying Circuits for Phase-Identified Channels1-20Figure 1-9Receiver Logic and Connections1-21Figure 1-10Phase-A Trip Selection1-22Figure 1-11Three-Pole Trip Selection1-23Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-4Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Front View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4DPM10-4-14Figure 4-5DNM10-4-16Figure 4-6DPM10-4-16Figure 4-7DPM11-4-16Figure 4-9ULM15-4-18Figure 4-10ULM15-4-18                              | Figure 1-2  |                                                      |                              |

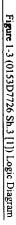

| Figure 1-4Elementary Diagram1-16Figure 1-5Dir. Comparison/Direct Trip Logic1-17Figure 1-6Weak Infeed/Repeat Key/LinePU/Out-of-Step Logic1-19Figure 1-7Trip and Reclose Logic1-19Figure 1-8Keying Circuits for Phase-Identified Channels1-20Figure 1-9Receiver Logic and Connections1-21Figure 1-10Phase-A Trip Selection1-22Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-8Figure 2-4PDS Function2-8Figure 2-5Connections for Communication Channels2-25Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-10ULM15-4-18Figure 4-10ULM1714-18                                                                                                 |             | Logic Diagram                                        | 1-13                         |

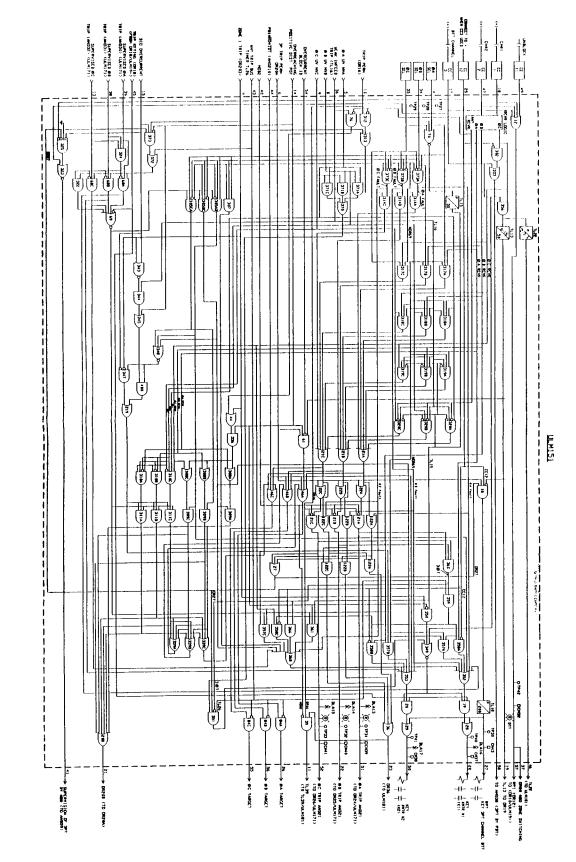

| Figure 1-5Dir. Comparison/Direct Trip Logic1-17Figure 1-6Weak Infeed/Repeat Key/LinePU//Out-of-Step Logic1-18Figure 1-7Trip and Reclose Logic1-19Figure 1-8Keying Circuits for Phase-Identified Channels1-20Figure 1-9Receiver Logic and Connections1-21Figure 1-10Phase-A Trip Selection1-22Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-6Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4DPM10-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-10ULM15-4-18                                                                                                                                |             | Elementary Diagram                                   | 1-16                         |

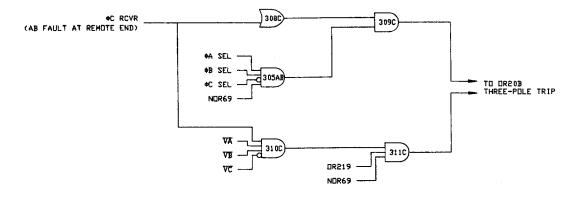

| Figure 1-6Weak Infeed/Repeat Key/LinePU/Out-of-Step Logic1-18Figure 1-7Trip and Reclose Logic1-19Figure 1-8Keying Circuits for Phase-Identified Channels1-20Figure 1-9Receiver Logic and Connections1-21Figure 1-10Phase-A Trip Selection1-22Figure 1-11Three-Pole Trip Selection1-23Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-6Figure 2-4PDX Function2-6Figure 2-5Connections for Communication Channels2-25Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions.3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-14Figure 4-4DNM10-4-14Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-10ULM1714-18                                                                                                                                        |             | Dir. Comparison/Direct Trip Logic                    | 1-17                         |

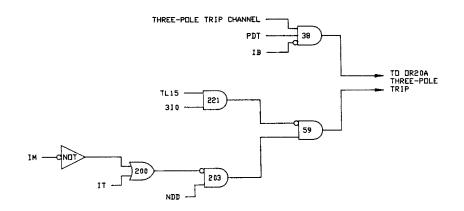

| Figure 1-7Trip and Reclose Logic1-19Figure 1-8Keying Circuits for Phase-Identified Channels1-20Figure 1-9Receiver Logic and Connections1-21Figure 1-10Phase-A Trip Selection1-22Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-6Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 4-1Module Locations4-10Figure 4-2ADM10-4-12Figure 4-3AEM10-4-13Figure 4-4AEM10-4-14Figure 4-5DNM10-4-15Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                          |             | Weak Infeed/Repeat Key/LinePU/Out-of-Step Logic      | 1-18                         |

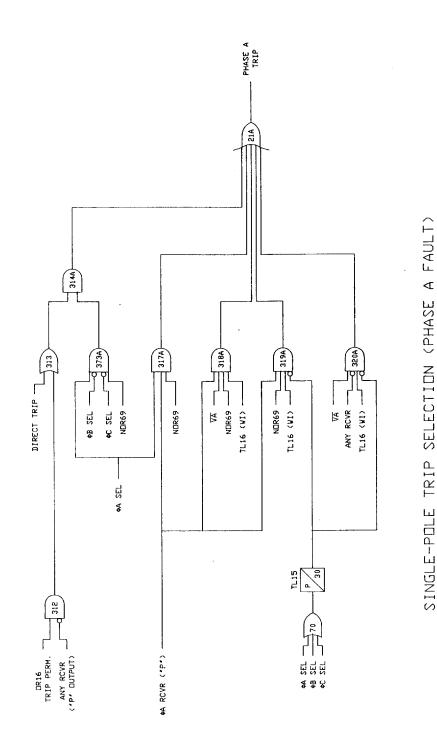

| Figure 1-8Keying Circuits for Phase-Identified Channels1-20Figure 1-9Receiver Logic and Connections1-21Figure 1-10Phase-A Trip Selection1-22Figure 1-11Three-Pole Trip Selection1-23Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-6Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 4-1Module Locations4-10Figure 4-2ADM10-4-12Figure 4-3AEM10-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-10ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                         |             | Trip and Reclose Logic                               | 1-19                         |

| Figure 1-9Receiver Logic and Connections1-21Figure 1-10Phase-A Trip Selection1-22Figure 1-11Three-Pole Trip Selection1-23Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-6Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-5DNM10-4-12Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-10ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                        |             | Keying Circuits for Phase-Identified Channels        | 1-20                         |

| Figure 1-10Phase-A Trip Selection1-22Figure 1-11Three-Pole Trip Selection1-23Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-6Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-14Figure 4-6DPM11-4-16Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-10ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                            |             | Receiver Logic and Connections                       | 1-21                         |

| Figure 1-11Three-Pole Trip Selection1-23Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-6Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 2-6Vary Inverse Time Overcurrent Curve2-28Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM10-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-16Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                 |             | Phase-A Trip Selection                               | 1-22                         |

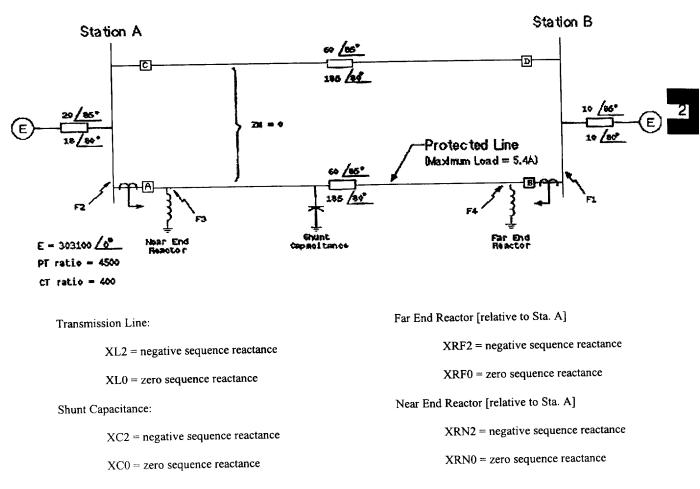

| Figure 2-1Sample Power System w/ Series Capacitors2-3Figure 2-2PDT Function2-4Figure 2-3PDB Function2-6Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 2-6Vary Inverse Time Overcurrent Curve2-28Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM10-4-14Figure 4-5DNM10-4-14Figure 4-6DPM10-4-16Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                                         |             | Three-Pole Trip Selection                            | 1-23                         |

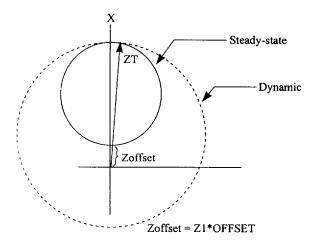

| Figure 2-2PDT Function2-4Figure 2-3PDB Function2-6Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 2-6Vary Inverse Time Overcurrent Curve2-28Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-14Figure 4-6DPM11-4-16Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                               | - Burt - II |                                                      | 25                           |

| Figure 2-2PDT Function2-4Figure 2-3PDB Function2-6Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 2-6Vary Inverse Time Overcurrent Curve2-28Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-14Figure 4-6DPM11-4-16Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                               | Figure 2-1  | Sample Power System w/ Series Canacitors             | 2-3                          |

| Figure 2-3PDB Function2-6Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 2-6Vary Inverse Time Overcurrent Curve2-28Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-5DNM10-4-14Figure 4-6DPM110-4-14Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                           |             | PDT Function                                         | 2-4                          |

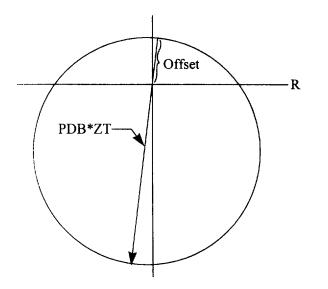

| Figure 2-4PDX Function2-8Figure 2-5Connections for Communication Channels2-25Figure 2-6Vary Inverse Time Overcurrent Curve2-28Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions.3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                |             | PDB Function                                         | <u>2</u> <del>-</del><br>2_6 |

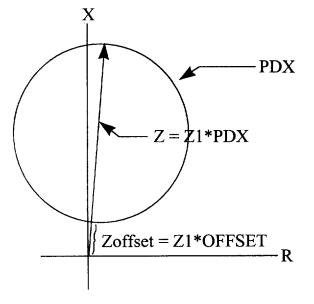

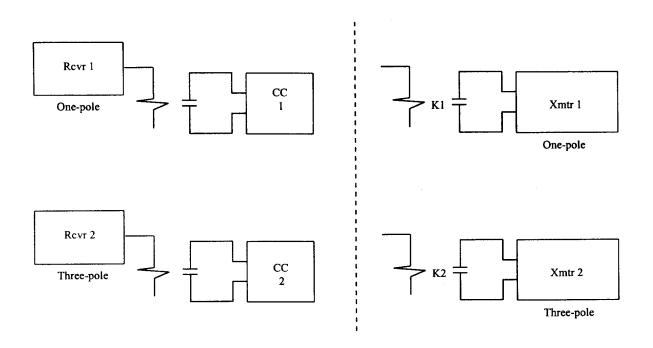

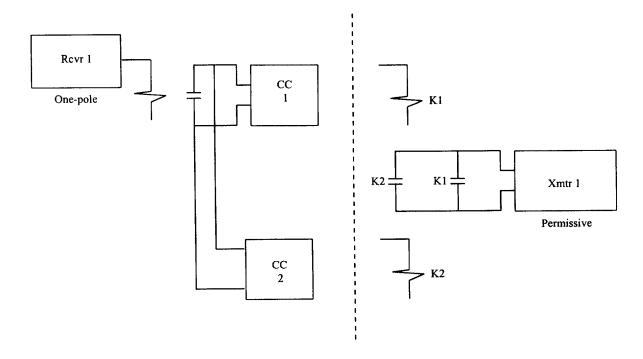

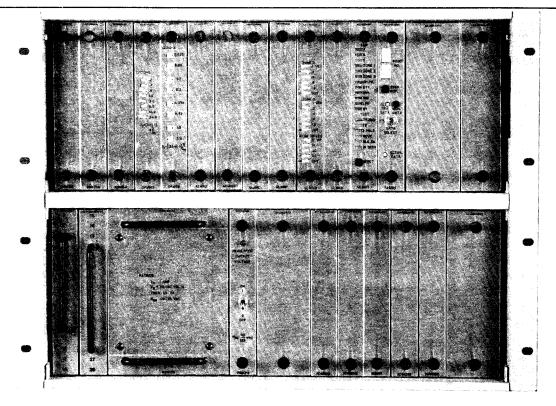

| Figure 2-5Connections for Communication Channels2-25Figure 2-6Vary Inverse Time Overcurrent Curve2-28Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                                          |             |                                                      |                              |

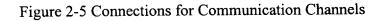

| Figure 2-6Vary Inverse Time Overcurrent Curve2-28Figure 3-1PLS Relaying System, Front View3-4Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             | Connections for Communication Channels               | 2_25                         |

| Figure 3-1PLS Relaying System, Front View.3-4Figure 3-2PLS Relaying System, Rear View.3-4Figure 3-3Outline and Mounting Dimensions.3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction).3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction).3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-15Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             | Vary Inverse Time Overcurrent Curve                  | 2-23                         |

| Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM10-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11501020    |                                                      |                              |

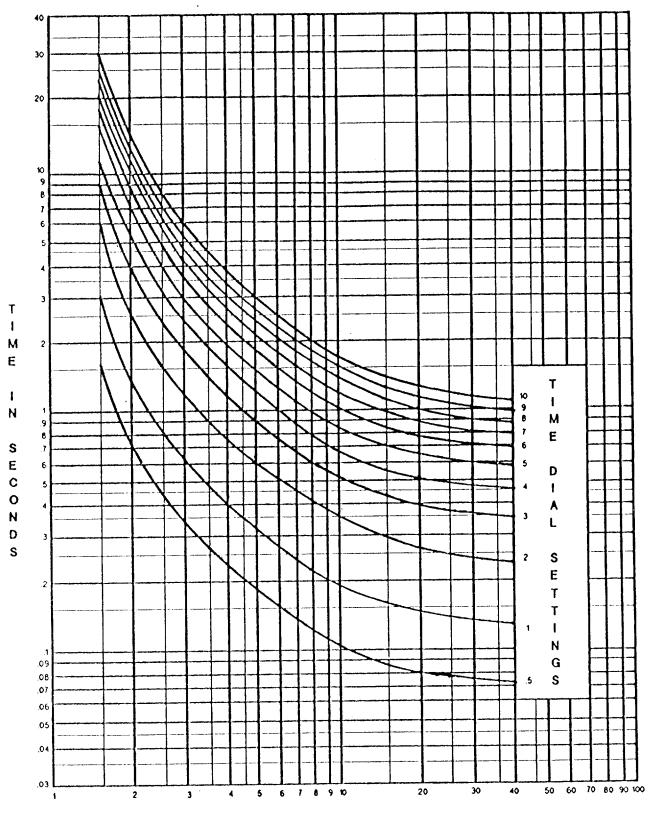

| Figure 3-2PLS Relaying System, Rear View3-4Figure 3-3Outline and Mounting Dimensions3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM10-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 3-1  | PLS Relaying System Front View                       | 3-4                          |

| Figure 3-3Outline and Mounting Dimensions.3-5Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |                                                      |                              |

| Figure 3-4XTM Connections for Dir. Ck. (Tripping Direction)3-9Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction)3-10Figure 4-1Module Locations4-10Figure 4-2ADM10-4-11Figure 4-3AEM10-4-12Figure 4-4AEM11-4-13Figure 4-5DNM10-4-14Figure 4-6DPM10-4-15Figure 4-7DPM11-4-16Figure 4-8TAM1014-17Figure 4-9ULM15-4-18Figure 4-10ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |                                                      |                              |

| Figure 3-5XTM Connections for Dir. Ck. (Non-Trip Direction) $3-10$ Figure 4-1Module Locations $4-10$ Figure 4-2ADM10- $4-11$ Figure 4-3AEM10- $4-12$ Figure 4-4AEM11- $4-13$ Figure 4-5DNM10- $4-14$ Figure 4-6DPM10- $4-15$ Figure 4-7DPM11- $4-16$ Figure 4-8TAM101 $4-17$ Figure 4-9ULM15- $4-18$ Figure 4-10ULM171 $4-19$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | XTM Connections for Dir Ck (Trinning Direction)      | 3_9                          |

| Figure 4-1       Module Locations       4-10         Figure 4-2       ADM10-       4-11         Figure 4-3       AEM10-       4-12         Figure 4-3       AEM11-       4-13         Figure 4-4       AEM11-       4-13         Figure 4-5       DNM10-       4-14         Figure 4-6       DPM10-       4-15         Figure 4-7       DPM11-       4-16         Figure 4-8       TAM101       4-17         Figure 4-9       ULM15-       4-18         Figure 4-10       ULM171       4-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             | XTM Connections for Dir. Ck. (Non-Trin Direction)    | 3-10                         |

| Figure 4-2       ADM10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | i iguio 5 5 | ATTA Connections for Diff. Ck. (1001-111) Direction/ |                              |

| Figure 4-2       ADM10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 4-1  | Module Locations                                     | 4-10                         |

| Figure 4-3       AEM10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |                                                      |                              |

| Figure 4-4       AEM11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |                                                      |                              |

| Figure 4-5       DNM10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |                                                      |                              |

| Figure 4-6       DPM104-15         Figure 4-7       DPM114-16         Figure 4-8       TAM1014-17         Figure 4-9       ULM154-18         Figure 4-10       ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 4-5  |                                                      |                              |

| Figure 4-7       DPM114-16         Figure 4-8       TAM1014-17         Figure 4-9       ULM154-18         Figure 4-10       ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |                                                      |                              |

| Figure 4-8       TAM101       4-17         Figure 4-9       ULM15-       4-18         Figure 4-10       ULM171       4-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |                                                      |                              |

| Figure 4-9       ULM154-18         Figure 4-10       ULM1714-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                                                      |                              |

| Figure 4-10 ULM171                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                                                      |                              |