## INSTRUCTIONS

## GEK-45478A

SUPERSEDES GEK-45478

AUXILIARY LOGIC UNIT

TYPE SLA52G

## GEK-45478

## CONTENTS

|       |       |        |              |      |       |     |          |    |    |    |   |   |   |   |   |   |     |   |   |     |    |   |   |   |   | _ | PAGE |

|-------|-------|--------|--------------|------|-------|-----|----------|----|----|----|---|---|---|---|---|---|-----|---|---|-----|----|---|---|---|---|---|------|

| DESCR | RIPTI | ON.    |              | •    |       |     |          |    | •  |    |   |   |   |   |   |   |     | • |   | •   |    | • |   |   |   |   | 3    |

| APPLI | CATI  | ON AN  | ND SE        | ETTI | NGS   |     |          |    |    |    |   |   |   |   |   |   |     |   | • |     |    |   |   |   |   |   | 3    |

| RATIN | IGS.  |        |              |      |       |     |          | •  |    | •  |   |   |   |   |   |   |     |   |   |     |    |   |   |   |   |   | 3    |

| BURDE | NS.   |        |              |      |       |     |          |    |    |    |   |   |   |   |   |   | • . |   |   |     |    |   |   |   |   |   | 3    |

| OPERA | TING  | PRIN   | IC I PI      | LES  |       | •   |          |    |    | •  | • |   | • |   |   | • |     |   |   |     |    |   | • |   |   |   | 3    |

| CONST | RUCT  | TION . | •, •         |      | • ; • |     |          |    |    |    |   |   | • | • |   | • |     |   |   |     | •, |   |   |   |   |   | 4    |

| INSTA | LLAT  | TION 1 | rest:        | s .  |       |     | •        |    |    |    |   |   |   |   |   |   |     |   |   | • . |    |   |   |   |   |   | 5    |

|       | Α.    | GENER  | RAL .        |      |       |     |          |    |    |    |   |   |   |   |   |   |     |   |   |     |    |   |   |   |   |   | 5    |

|       | В.    | OPER#  | ITIO1        | NAL  | CHE   | CKS | <b>.</b> |    |    |    |   |   |   |   |   |   |     |   |   | •   |    |   |   |   |   |   | 5    |

|       | С.    | TEST   | CARI         | D AD | APT   | ΞR  |          |    |    |    | • |   |   |   |   |   |     |   |   |     |    |   |   |   |   |   | 5    |

|       | D.    | TIMER  | ≀ AD         | JUST | MENT  | ΓS  | ٨N       | ID | TE | ST | S |   |   |   |   |   |     |   |   |     |    |   |   |   |   |   | 5    |

|       | Ε.    | OVERA  | ALL E        | EQUI | PME   | T   | TE       | ST | S  |    |   |   |   |   |   |   |     |   |   | •   |    |   |   |   |   |   | 5    |

| MAINT | ENAN  | ICE    | , <b>.</b> . |      |       |     |          |    | •  | •  |   |   | • |   |   | ÷ |     |   |   |     |    |   |   |   |   | • | 6    |

|       | Α.    | PERIC  | DIC          | TES  | TS.   |     |          |    |    |    | • |   |   |   |   |   |     |   |   |     |    |   |   |   |   |   | 6    |

|       | В.    | TROUE  | BLE S        | SH00 | TING  | à.  |          |    |    |    |   |   |   |   |   |   |     |   |   |     |    |   |   |   |   |   | 6    |

|       | С.    | SPARE  | : PAF        | RTS  |       |     |          |    |    |    |   |   |   |   |   |   |     |   |   |     |    |   | • |   |   |   | 6    |

|       |       |        |              |      |       | •   | •        | •  | •  | •  | • | • | • | • | • | • | •   | • | • | •   | •  | • | • | • | • | ٠ | U    |

#### AUXILIARY LOGIC UNIT

#### TYPE SLA52G

#### DESCRIPTION

The SLA52G unit is an auxiliary logic unit in blocking or unblocking schemes using frequency shift channel equipment. It is usually used with a type SLYP positive sequence distance unit, a type SLCN negative sequence directional overcurrent unit, a type SLAT output tripping unit, a type SSA power supply and a test panel.

The SLA52G has appropriate interconnections for use with a type SLAT54F auxiliary and tripping unit when applied in single pole tripping and reclosing schemes.

The SLA52G is designed with considerable flexibility to accommodate various types of schemes such as blocking, unblocking, permissive transfer tripping, or combined schemes such as an unblocking scheme combined with a direct transfer trip scheme. Provision is made for various auxiliary tripping circuits which may be supplied initially or easily added later in the field. These optional circuits include direct tripping overcurrent and distance functions, line "pickup" circuitry, "weak infeed" trip circuitry, out-of-step tripping or blocking circuitry, and second zone backup timing circuitry.

#### APPLICATION AND SETTINGS

Because of the flexibility of the type SLA52G, the application and settings will vary with the particular type of scheme in which it is used. Refer to the overall logic diagram description for application and setting information for the particular scheme in which the SLA52G is used.

#### RATINGS

The Type SLA52G relay is designed for use in an environment where the ambient temperature outside the relay case is between  $-20^{\circ}$ C and  $+65^{\circ}$ C.

The Type SLA52G relay requires a  $\pm 15$ VDC power source which can be obtained from a type SSA50/51 power supply.

Each contact converter in this relay has a link for selecting the proper voltage for the coil circuit of the contact converter. The three available voltage taps are for 48, 125 or 250 VDC.

#### BURDENS

The SLA52G presents a burden of 350 ma. to the +15 VDC supply of the Type SSA power supply.

Each contact converter, when energized, will draw approximately 10 ma. from the station battery, regardless of the station battery voltage.

#### OPERATING PRINCIPLES

The functions included in the Type SLA52G relay involve basic logical operations (AND, OR, NOT) where the presence or absence of signals, rather than their magnitude, controls the operation. Signals are measured with respect to a reference bus accessible at TP1. In general, a signal below 1 VDC represents an OFF OR LOGIC ZERO condition; an ON OR LOGIC ONE condition is represented by a signal of approximately +15 VDC.

These instructions do not purport to cover all details or variations in equipment nor to provide for every possible contingency to be met in connection with installation, operation or maintenance. Should further information be desired or should particular problems arise which are not covered sufficiently for the purchaser's purposes, the matter should be referred to the General Electric Company.

To the extent required the products described herein meet applicable ANSI, IEEE and NEMA standards; but no such assurance is given with respect to local codes and ordinances because they vary greatly.

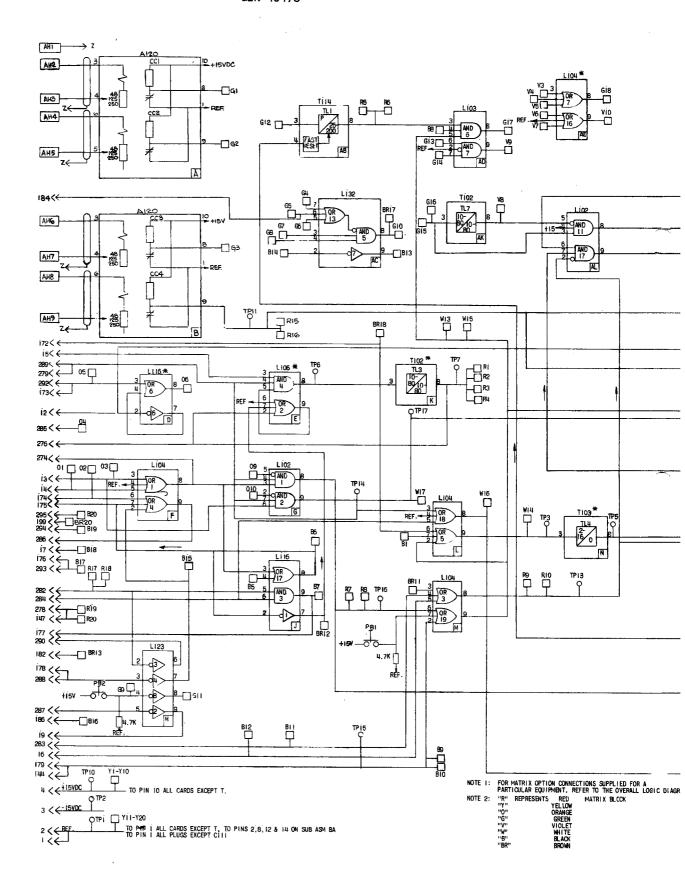

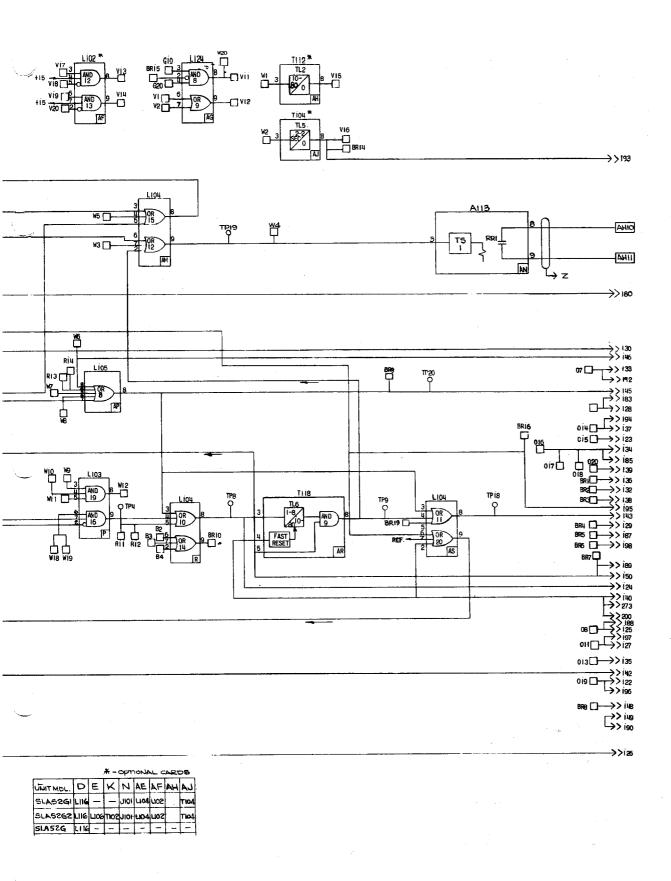

The symbols used on the internal connection diagram Figure 1 are explained by the legend shown in Figure 2.

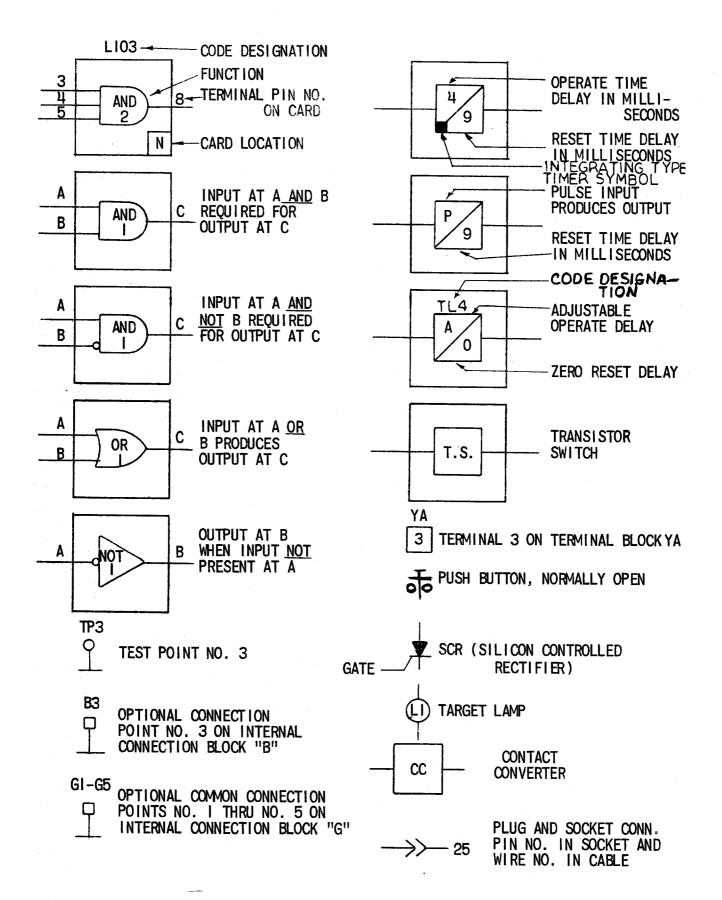

The matrix blocks shown on the internal connections diagram of the SLA52G are connected by jumpers at the factory. These connections are used to implement the logic arrangement shown on the associated overall logic diagram. These matrix jumpers are listed on the associated option chart. A typical option chart for the Type SLA52G relay is shown in Figure 3. Some of the matrix block connections may be customer options. These connections will then be shown as optional connections on the overall logic and must be selected by the user before the unit is placed in service.

The purpose of the contact converters (CC1, CC2, CC3, CC4) included in the Type SLA52G relay is to convert a contact operation into a signal that is compatible with the logic circuitry of the relay. When the external contact is closed, a +15VDC signal is produced by the contact converter. The function of each contact converter depends upon the particular relaying scheme in which it is employed.

The Type SLA52G relay has provisions for up to 18 outputs suitable for driving a Type DLA data logging amplifier unit. Any matrix block point which is not used as a logic connection may be monitored by connecting a lead from the 411 or 421 socket to the block. If it is desired to monitor a matrix point which is used as a logic connection, wires 417 to 420 and 427 to 430 may be used. These points have two leads with taper tips which are used to replace the logic jumper. This provides the logic signal path and also a signal for the DLA unit. Any factory selected DLA points are listed on the option chart.

The Type SLA52G relay includes a contact interface between the relaying equipment and the associated channel.

#### CONSTRUCTION

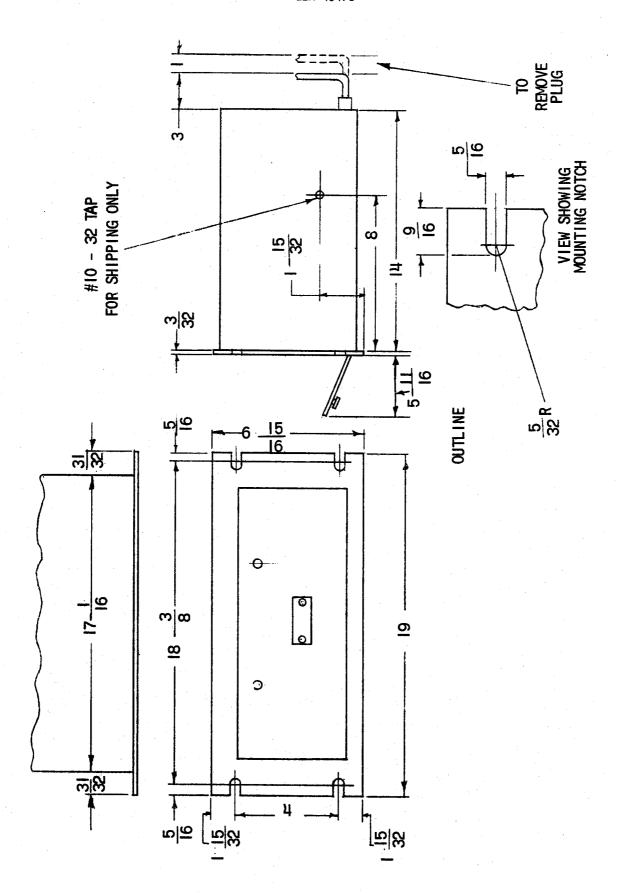

The SLA52G relay is packaged in an enclosed metal case with hinged front covers and removable top cover. The outline and monitoring dimensions of the case and the physical location of the components are shown in Figures 4 and 5 respectively.

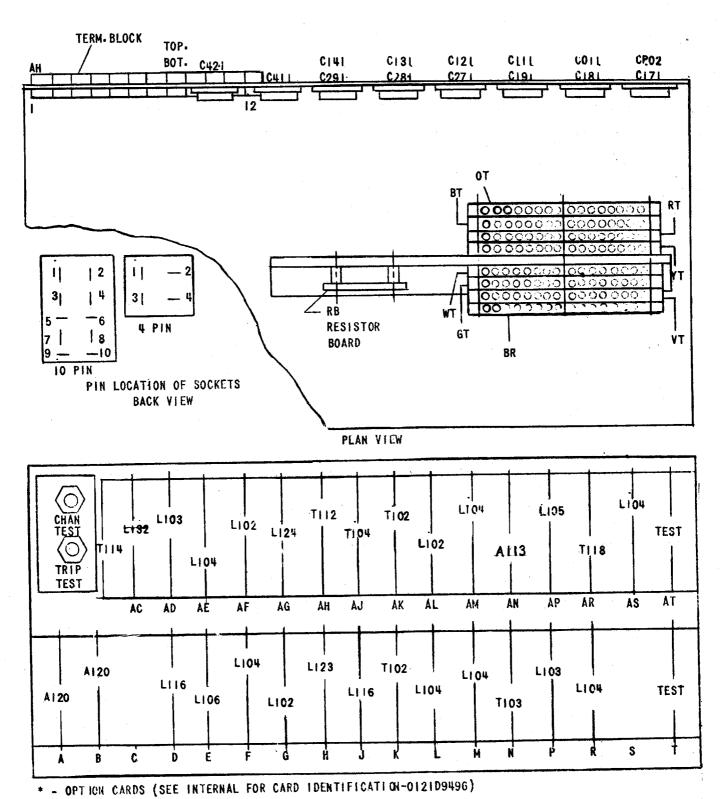

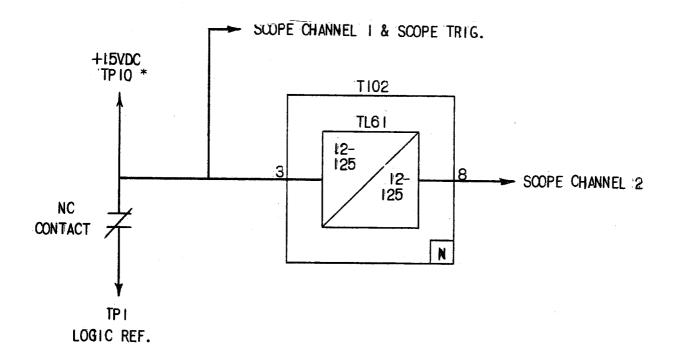

The SLA52G relay contains printed circuit cards identified by a code number such as All1, Tl02, Ll04 where A designates auxiliary function, T designates time delay function, and L designates logic function. The printed circuit cards plug in from the front of the unit. The sockets are marked with letter designations or "addresses" (D, E, F, etc.) which appear on the guide strips in front of each socket, on the component location drawing, on the internal connection diagram and on the printed circuit card. The test points (TP1, TP2, etc.) shown in the internal connection diagram are connected to instrument jacks on a test card in position T or AT with TP1 at the top of the AT card. TP10 is tied to +15 VDC through a 1.5K resistor. This resistor limits the current when TP10 is used to supply a logic signal.

Logic options in the SLA52G relay are selectable by means of jumper wires with taper tip pins on each end which are used to interconnect the matrix block points. These matrix blocks are located in the rear of the unit as shown in Figure 5. The top cover of the relay must be removed to make the blocks accessible. The taper tip jumpers should be inserted and removed using the special tools which are supplied with each equipment. The green (G), black (B), white (W), violet (V), orange (O) and brown (BR) matrix blocks have 20 individual matrix points. The red (R) block has 20 points which are grouped in 10 pairs. The yellow (Y) block has 20 points, which are grouped in 2 sets of 10 common points; YI to Y10 are connected to +15 VDC, Y11 to Y20 are connected to reference.

These relays will normally be supplied as a part of a static relay equipment, mounted in a rack or cabinet with other static relays and test equipment. Immediately upon receipt of a static relay equipment, it should be unpacked and examined for any damage sustained in transit. If injury or damage resulting from rough handling is evident, file a damage claim at once with the transportation company and promptly notify the nearest General Electric Sales Office.

Reasonable care should be exercised in unpacking the equipment. If the equipment is not to be installed immediately, it should be stored indoors in a location that is free from moisture, dust, metallic chips, and severe atmospheric contaminants.

Just prior to final installation the shipping support bolt should be removed from each side of all relay units, to facilitate possible future unit removal for maintenance. These shipping support bolts are approximately 8 inches back from the relay front panel. Static relay equipment, when supplied in swing rack cabinets, should be securely anchored to the floor or to the shipping pallet to prevent the equipment from tipping over when the swing rack is opened.

#### GEK-45478

#### INSTALLATION TESTS

If the SLA52G relay that is to be tested is installed in an equipment which has already been connected to the power system, disconnect the outputs in the associated Type SLAT relay from the system.

#### CAUTION

THE LOGIC SYSTEM SIDE OF THE DC POWER SUPPLY USED WITH MOD III STATIC RELAY EQUIPMENT IS ISOLATED FROM GROUND. IT IS A DESIGN CHARACTERISTIC OF MOST ELECTRONIC INSTRUMENTS THAT ONE OF THE SIGNAL INPUT TERMINALS IS CONNECTED TO INSTRUMENT CHASSIS. IF THE INSTRUMENT USED TO TEST THE RELAY EQUIPMENT IS ISOLATED FROM GROUND, ITS CHASSIS MAY HAVE AN ELECTRICAL POTENTIAL WITH RESPECT TO GROUND. THE USE OF A TEST INSTRUMENT WITH A GROUNDED CHASSIS WILL NOT AFFECT THE TESTING OF THE EQUIPMENT. A SECOND GROUND CONNECTION TO THE EQUIPMENT, SUCH AS A TEST LEAD INADVERTENTLY DROPPING AGAINST THE RELAY CASE, MAY CAUSE DAMAGE TO THE LOGIC CIRCUITRY. NO EXTERNAL TEST EQUIPMENT SHOULD BE LEFT CONNECTED TO THE STATIC RELAYS WHEN THEY ARE IN PROTECTIVE SERVICE, SINCE TEST EQUIPMENT GROUNDING REDUCES THE EFFECTIVENESS OF THE ISOLATION PROVIDED.

#### A. GENERAL

The SLA52G relay is supplied from the factory either mounted in a static relay equipment or as a separate unit associated with measuring relays, a Type SSA power supply, and some form of channel equipment. All relay units for a given terminal of static relaying equipment are tested together at the factory, and each unit will have the same summary number stamped on its nameplate.

Timers should be set for the operating and reset times indicated on the associated overall logic diagram. Where a time range is indicated on the overall logic diagram, the timer should be set for the value recommended for that function in the descriptive writeup accompanying the overall logic diagram. Where a setting depends upon conditions encountered on a specific application, this is so stated and the factors influencing the choice of setting are described. The procedure for checking and setting the timers is described in a later section.

#### B. OPERATIONAL CHECKS

Operation of the SLA52G unit can be checked by observing the signals at the twenty test points (TP1 to TP20) in the SLA52G by observing the operation of the associated channel equipment, or by observing the output functions in the associated Type SLAT tripping relay. The test points are located on two test cards in positions T and AT, and are numbered 1 to 20 from top to bottom. TP1 is the reference bus for the logic circuit; TP10 is at +15 VDC. The remaining points are located at various strategic points throughout the logic as shown on the internal connection diagram Figure 1. Test point voltages can be monitored with a portable high impedance voltmeter, the voltmeter on the test panel of the associated equipment, or an oscilloscope.

Operation of any logic function may be checked by supplying the correct inputs to the card. This is accomplished by placing the card under test in a card extender, removing the cards which normally supply the input signals, and then connecting the card inputs to either TP10 or TP1. An output should be produced when the proper combination of inputs is supplied.

#### C. TEST CARD ADAPTER

The test card adapter provides a convenient means of gaining access to any pin of a particular card. Detailed information on the use of the test adapter card is included in the card instruction book GEK-34158.

#### D. TIMER ADJUSTMENTS AND TESTS

When the time delay cards are to be adjusted or checked, an oscilloscope that can display two traces simultaneously and that has a calibrated horizontal sweep should be used.

In order to test the timer cards it is necessary to remove the card which supplies the input to the timer and to place the timer card in a card adapter. The card adapter allows access to the input and output of the timer if they are not brought out on test points. The timer test circuit is shown in Figure 6. Opening the N.C. contact causes the output to step up to +15 VDC after the pickup delay of the timer. To increase the pickup time turn the upper potentiometer on the timer card clockwise; to decrease the time delay setting of card, turn the upper potentiometer counterclockwise. If the timer card is provided with a Variable reset delay, it can be adjusted by the lower potentiometer on the timer card (CW increases reset time).

#### E. OVERALL EQUIPMENT TESTS

After the SLA52G relay and the associated static relay units have been individually cali-rated and tested for the desired settings, a series of overall operating circuit checks is advisable.

The elementary, overall logic, and logic description for the specific job will be useful for determining the overall operation of the scheme.

Overall equipment tests can be performed by applying AC current and voltages to the measuring units as specific in the instruction book for the measuring units and checking that proper outputs are obtained from the associated SLAT when the measuring units operate.

#### MAINTENANCE

#### A. PERIODIC TESTS

It should be sufficient to check the outputs produced at test points in the SLA52G when periodic calibration tests are made on the associated measuring units, for example the phase and ground relay in line relaying scheme. No separate periodic tests on the SLA52G itself should be required.

#### B. TROUBLE SHOOTING

In any trouble shooting of equipment, it should first be established which unit is functioning incorrectly. The overall logic diagram supplied with the equipment shows the combined logic of the complete equipment and the various test points in each unit. By signal tracing, using the overall logic diagram and the various test points, it should be possible to quickly isolate the trouble.

A test adapter card is supplied with each static relay equipment to supplement the prewired test points on the test cards. Use of the adapter card is described in the card instruction book GEK-34158.

A dual-trace oscilloscope is a valuable aid to detailed trouble shooting, since it can be used in determing phase shift, operate and reset times as well as input and output levels. A portable dual-trace oscilloscope with a calibrated sweep and trigger facility is recommended.

#### C. SPARE PARTS

To minimize possible outage time, it is recommended that a complete maintenance program should include the stocking of at least one spare card of each type. It is possible to replace damaged or defective components on the printed circuit cards, but great care should be taken in soldering so as not to damage or bridge-over the printed circuit busses, or overheat the semi-conductor components. The repaired area should be recovered with a suitable high-dielectric plastic coating to prevent possible breakdowns across the printed busse due to moisture and dust. The wiring diagrams for the cards in the SLA52G relay are included in the card book GEK-34158.

## NOTES

FIG. 1 (0136D3447-3) INTERNAL CONN

TIONS DIAGRAM FOR THE TYPE SLAT52G

FIG. 2 (0227A2047-0) INTERNAL CONNECTION DIAGRAM LEGEND

## PLT CABLE PLUG

## (5)=LOGIC FUNCTION CARD PIN NUMBER

| MATRIX     | BLOCK       | LOGIC FU | NCTION   | MATRIX<br>JUMPE | BLOCK     | LOGIC FL  | UNCTION  |  |  |

|------------|-------------|----------|----------|-----------------|-----------|-----------|----------|--|--|

| FROM       | TO          | FROM     | TO       | FROM            | TO        | FROM      | TO       |  |  |

| G8         | YI          | +15      | AND 5(4) | BR/2            | B18       | NOTI (7)  | PL17     |  |  |

| R19        | Y2          | +15      | PL 147   | BIZ             | 010       | PL16      | AND2(2)  |  |  |

|            |             |          |          | 04              | WB        | PL285     | OR8(6)   |  |  |

|            |             |          |          | BRIG            | 015       | PL12      | PL123    |  |  |

| <b>V</b> 5 | Y11*        | REF      | OR7(5)   | 06              | <b>G7</b> | OR6(8)    | AND 5(3) |  |  |

| RII        | YII         | REF      | OR10(5)  | 910             | BI        | AND 5(8)  | OR5 (7)  |  |  |

| W3         | Y12*        |          | OR12(7)  | BRIO            | 013*      | OR14 (9)  | PL135    |  |  |

| BR15       | Y12         | REF      | AND 8(2) | BRIO            | 019*      | OR14 (9)  | PL122    |  |  |

| 45         | Y13*        | REF      | OR13(6)  | GI              | G12       | cc1 (8)   | TLI (3)  |  |  |

| G6         | Y13         | REF      | OR13(5)  | <b>R</b> 5      | B5        | TLI (8)   | OR17(4)  |  |  |

| <b>B3</b>  | Y14*        | REF      | OR14(7)  | R6              | 913       | TL1 (8)   | AND 7(6) |  |  |

| R13        | Y14         | REF      | OR8(4)   | W16             | 614       | OR18 (8)  | AND 7(7) |  |  |

| BRII       | <b>Y15*</b> | REF      | OR3(3)   | V9              | WI        | AND 7(9)  | TL2 (3)  |  |  |

| W7         | Y15         | REF      | OR8(5)   | V15             | <b>V3</b> | TL2 (8)   | oR7 (3)  |  |  |

| W5         | <b>Y16*</b> | REF      | OR15(4)  | G18             | W6        | OR7 (8)   | OR8(3)   |  |  |

| 02         | 716         | REF      | OR4(6)   | B7              | B9        | AND3 (9)  | OR19(2)  |  |  |

| BRIS       | Y17*        | REF      | 0R5(6)   | W15             | BR4       | OR19 (9)  | PL129    |  |  |

| 09         | <b>Y17</b>  | REF      | AND 1(5) | G17             | V4        | AND 6 (8) | OR7 (4)  |  |  |

| BR19       | Y18         | REF      | OR11(5)  | W14             | BRI       | OR5 (9)   | PL136    |  |  |

|            |             |          |          | RIO             | 020       | OR3 (8)   | PL139    |  |  |

| BR8        | 017         | PL148    | PL134    | W4              | G19       | OR12(9)   | AND 8(3) |  |  |

| 012        | G20         | PL128    | AND8(4)  | W20             | BR3       | AND 8 (8) |          |  |  |

| G16        | BKZ         | TL7 (3)  | PL132    | R15             | VI        | (AN 7)    | OR9(6)   |  |  |

| GZ         | B4          | CCZ(9)   | OR14(2)  | RI7             | V2        | (AN 8)    | OR9(7)   |  |  |

| RI         | BZ          | TL3(8)   |          | 014             | 018       | PL137     | PL134    |  |  |

| V12        | W18         | OR9(9)   | ANDG(C)  | G15             | W19       | ANDILE)   | TL7(3)   |  |  |

| *USE JU    |             | 0227AZ   |          | V8              | <b>G4</b> | TL7(8)    | OR13(7)  |  |  |

FIG. 4 (0227A2037-0) OUTLINE AND MOUNTING DIMENSIONS FOR THE TYPE SLA52G RELAY

FIG. 5 (0257A8776-0) COMPONENT AND CARD LOCATIONS FOR THE SLA52G RELAY

\* THE 15VDC SIGNAL AT PIN 10 HAS A CURRENT LIMITING RESISTOR MOUNTED ON THE TEST CARD.

# GENERAL ELECTRIC COMPANY POWER SYSTEMS MANAGEMENT BUSINESS DEPT. PHILADELPHIA, PA. 19142